you should know what all of the following things are:

concepts

combinational logic:

state elements:

if you don't know what these things are, ask me - we need to clear these things up really soon. :)

a single cycle cpu executes each instruction in one cycle. in other words, one cycle is needed to execute any instruction. in other words, our cpi is 1.

each cycle requires some constant amount of time. this means we will spend the same amount of time to execute every instruction [one cycle], regardless of how complex our instructions may be. to ensure that our processor operates correctly, our slowest instruction must be able to complete execution correctly in one clock tick. this is the big disadvantage of single cycle cpu's: the machine must operate at the speed of the slowest instruction. the big advantage of single cycle cpu's is that they are easy to implement.

here's an outline of all the things that happen on each cycle in our single cycle cpu:

this would also make a good outline for an emulator.

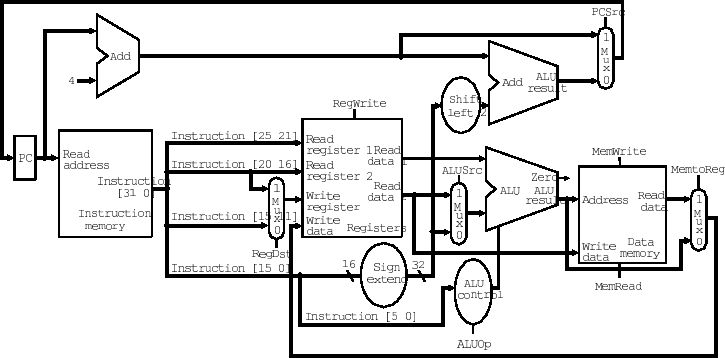

here's our single cycle datapath:

get familiar with the tables on the inside back cover of your book. they're very, very helpful when you're doing this sort of thing.

the datapath is the plumbing of the processor. it shows all the ways bits can flow from one component to another. for example, on our sample datapath, you can see that we always read registers rs and rt. it is impossible for us to read register rd. there are many important wires that look like they aren't connected to anything [regdst, regwrite, alusrc, etc]. these are "control signals," and they are driven by the control logic.

if i point to any component on the datapath, you should be able to tell me what it is and why we need it.

control, as its name implies, controls the datapath. whenever there is a decision to be made, control is responsible for making the right decision. for example: are we using our alu to add or subtract? do we write to register rt or rd? do we want to read from or write to memory?

so... how does control figure out what needs to be done? it depends entirely on the instruction we are executing. given any instruction, control must direct the flow of bits through the datapath so that the instruction executes properly. in other words, the values of our control signals depend on the opcode and function code of the instruction that we are currently executing.

pseudocode for the control logic should look something like this:

switch(opcode) {

case 0: // alu operation - we need to look at the function code

switch(function_code) {

case 32: // add

regdst=0;

alusrc=1;

pcsrc=1;

aluop=add;

memread=0;

memwrite=0;

memtoreg=0;

regwrite=1;

break;

// more function codes...

}

break;

// more opcodes...

}

if i give you any opcode and function code, you should be able to tell me what the values of all the control signals should be.

you should also be able to convert this pseudocode into a nasty pile of combinational logic ['and' and 'or' gates, etc] if asked to. remember, opcode and function code go in one end, values for the control signals come out the other end.

okay, now that we [hopefully] understand how our single cycle cpu works, we will try the following exercises:

if we are executing an addi instruction, what are the values of the control signals?

what is the "sign extender", and why do we need it on our datapath? why can't we just use all zeroes for the top 16 bits of the extended immediate?

i want to support the mips left shift operation. [sll,

refer to the inside cover of the back of your book]. assume that the

alu can do shift operations. what new datapath elements, if any, are

required? how do we set the control signals for a left shift

instruction?

i want a "conditional move" instruction:

cmov $1, $2,

$3 means "copy the value in register 2 into register 1 if

register 3 is nonzero". what new datapath elements, if any, are

required? how do we set the control signals for a conditional move

instruction?

brad specifically asked that i go over the autoincrement problem again [question 1 on "modifying cpu examples"]. we want to add a new type of store instruction that also increments register rs by 4 in addition to performing the store. show datapath modifications and control logic.

how about brad's mem-reg instructions? [question 4 on "modifying cpu

examples"]. given an instruction like add $5, offset($6),

we need to add the value in register $5 with the data stored at memory

location offset+$6, and store the sum in register

$5. show datapath modifications and control logic.