INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS TO

# $\begin{array}{c} INTERNATIONAL \\ ROADMAP \\ FOR \\ DEVICES AND SYSTEMS^{^{TM}} \end{array}$

# 2022 EDITION

# **EXECUTIVE SUMMARY**

THE IRDS<sup>TM</sup> IS DEVISED AND INTENDED FOR TECHNOLOGY ASSESSMENT ONLY AND IS WITHOUT REGARD TO ANY COMMERCIAL CONSIDERATIONS PERTAINING TO INDIVIDUAL PRODUCTS OR EQUIPMENT.

© 2022 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Wi-Fi® and Wi-Fi Alliance® are registered trademarks of Wi-Fi Alliance.

LTE<sup>TM</sup> is a Trademark of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners.

The IEEE emblem is a trademark owned by the IEEE.

"IEEE", the IEEE logo, and other IEEE logos and titles (IRDS<sup>TM</sup>, IEEE 802.11<sup>TM</sup>, IEEE P1785<sup>TM</sup>, IEEE P287<sup>TM</sup>, IEEE P1770<sup>TM</sup>, IEEE P149<sup>TM</sup>, IEEE 1720<sup>TM</sup>, etc.) are registered trademarks or service marks of The Institute of Electrical and Electronics Engineers, Incorporated. All other products, company names or other marks appearing on these sites are the trademarks of their respective owners. Nothing contained in these sites should be construed as granting, by implication, estoppel, or otherwise, any license or right to use any trademark displayed on these sites without prior written permission of IEEE or other trademark owners.

iPhone is a trademark of Apple, Inc.

NPD's name, NPD's logo, and all related names, logos, product and service names, designs, and slogans are trademarks of The NPD Group, Inc.

ZOOM is a trademark of Zoom Video Communications, Inc.

# **Table of Contents**

| 1. | Intro | duction                                                                             | 1  |

|----|-------|-------------------------------------------------------------------------------------|----|

|    | 1.1.  | 2021/2022 Industry Highlights and Key Messages from the 2022 IRDS                   | 3  |

|    | 1.2.  | The New Ecosystem of the Electronics' Industry                                      | 18 |

|    | 1.3.  | Beyond Dimensional Scaling                                                          | 34 |

|    | 1.4.  | Quantum Information Processing (QIP)                                                | 34 |

| 2. | Road  | Imap Process and Structure                                                          | 35 |

|    | 2.1.  | Roadmap Process                                                                     | 35 |

|    | 2.2.  | IRDS International Focus Teams (IFTs) structure and description                     | 35 |

| 3. | Over  | all Roadmap Drivers—ORSC and ORTC                                                   | 41 |

|    | 3.1.  | System Performance Considerations                                                   | 41 |

|    | 3.2.  | Overall Roadmap Systems and Technology Characteristics (ORSC and ORTC)              | 43 |

| 4. | Gran  | d Challenges                                                                        | 46 |

|    | 4.1.  | In the Near-term                                                                    | 46 |

|    | 4.2.  | In the Long-term                                                                    | 51 |

| 5. |       | rical Evolution of the Roadmap Methodology and its Effect on the ronics Industry    | 53 |

|    | 5.1.  | Moore's Law                                                                         |    |

|    | 5.2.  | The Dawn of the New Computer Industry                                               | 54 |

|    | 5.3.  | SoC and SiP                                                                         | 59 |

|    | 5.4.  | Power Challenge                                                                     | 60 |

|    | 5.5.  | Consequences of Frequency Limitations                                               | 60 |

|    | 5.6.  | Internet of Things, Internet of Everything (IoT, IoE)                               | 64 |

|    | 5.7.  | The 3 Eras of Scaling                                                               | 65 |

| 6. | Prac  | tical Considerations                                                                | 69 |

| 7. | The   | Challenge of Quantum Computing                                                      | 72 |

| 8. | Acro  | nyms/Abbreviations                                                                  | 73 |

| 9. | Appe  | endix                                                                               | 76 |

|    | 9.1.  | Appendix A—IFT Chapter and White Paper Files Links                                  |    |

|    | 9.2.  | Appendix B—Overall Roadmap Characteristics (ORSC and ORTC) Source Information Links | 70 |

# **List of Figures**

| Figure ES1        | IRDS Scope                                                                                                           | 2  |

|-------------------|----------------------------------------------------------------------------------------------------------------------|----|

|                   | A. Compilation of relevant trends associated with the ectronics industry                                             | 3  |

| Figure ES2        | B. Forecasted GDP, Smartphones, PC and Light Vehicle trends                                                          | 4  |

| Figure ES3        | Semiconductor content in Electronics Systems doubled in 20 years                                                     | 5  |

| Figure ES4        | Growth of units resumes at the historical rate of 8.4%CAGR                                                           | 6  |

| Figure ES5        | Factory utilization exceeded 95% in 2021!                                                                            | 6  |

| Figure ES6        | IC wafer capacity growing above 8% yearly rate in 2021 and 2022                                                      | 7  |

| •                 | A. While semiconductor delivers recovered many other items are ill experiencing major delays in the supply chain     | 8  |

| Figure ES7        | B. Shipments of motor vehicle approaching getting back on track                                                      | 8  |

|                   | Semiconductor forecasted growth may swing from exuberance collapse                                                   | 9  |

| Figure ES9        | Optoelectronics growing at 13% CGR for past 10 years                                                                 | 10 |

| Figure ES10       | Shipments of EUV lithography scanners continued to grow in 2021                                                      | 11 |

|                   | A. Devices will continue to aggressively scale in the next five years.  ogic transition to 3D is still aimed at 2025 | 12 |

|                   | B. Transitions from 2D to 3D device architecture in NAND and ogic is progressing as predicted by 2013 ITRS           | 12 |

|                   | Transistor 2003-2025 evolution: From 2D Equivalent scaling to D Power scaling                                        | 13 |

| Figure ES11<br>th | D. Vertical transistors and nanoribbons are progressively entering e logic technology arsenal                        | 13 |

|                   | E. 3D NAND evolution: from 32 layers in 2025 to over 1000 layers                                                     | 14 |

| Figure ES12       | R&D spending remains under control                                                                                   | 15 |

| Figure ES13       | Scaling progressing unabated with EUV technology                                                                     | 15 |

|                   | Communication traffic growing close to doubling every year for the reseeable future                                  | 16 |

| Figure ES15       | Rate of investment in hyperdata centers doubled in 5 years                                                           | 17 |

|                   | Performance of devices beyond CMOS continues to improve towards pal                                                  |    |

| Figure ES17       | Quantum centers require fast network for ubiquitous access                                                           | 18 |

| Figure ES18       | Pandemic spurred PC sales in 2020-2021!                                                                              | 19 |

| Figure ES19       | Sales of smartphones declined in 2020                                                                                | 19 |

| Figure ES20       | Clock frequency limited to less than 10GHz by power wall                                                             | 20 |

| Figure ES21       | Facial Biometrics is becoming an intrinsic part of society security                                                  | 21 |

|                   | EUV source power exceeding 200W and uptime of over 80% opened e way for EUV introduction into manufacturing          | 22 |

| •                 | Mask number using multiple 193 nm lithography doubled in the past<br>/e years                                        | 23 |

| Figure | ES24 | 3D NAND evolution: from 32 layers in 2015 to over 1000 layers by 2030                                                                                              | 24 |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure | ES25 | Original technology node definition                                                                                                                                | 25 |

| Figure | ES26 | Industry "adaptation" of technology node definition                                                                                                                | 25 |

| Figure | ES27 | IRDS comprehensive technology node definition                                                                                                                      | 26 |

| Figure | ES28 | Devices will continue to aggressively scale in the next 5 years                                                                                                    | 26 |

| Figure |      | Consistent definition and trend of metal half-pitch reported by ASML nd IRDS                                                                                       | 27 |

| Figure |      | Metal pitch scaling exceeding expectation in 2020!                                                                                                                 |    |

| _      |      | Data center growth continues to accelerate                                                                                                                         |    |

| -      |      | Traffic within data center is main limiting factor                                                                                                                 |    |

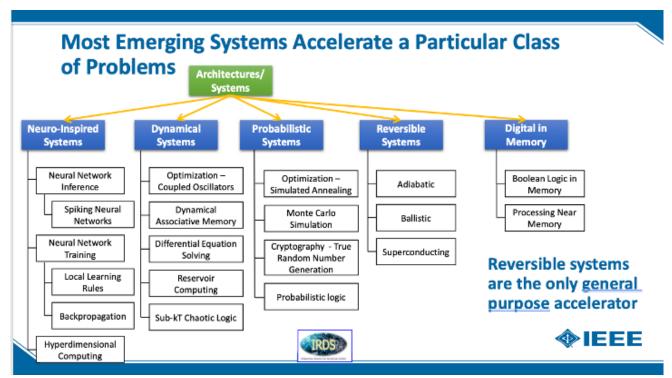

| -      | ES33 | Multiple specialized architectures are emerging to solve pecific problems                                                                                          |    |

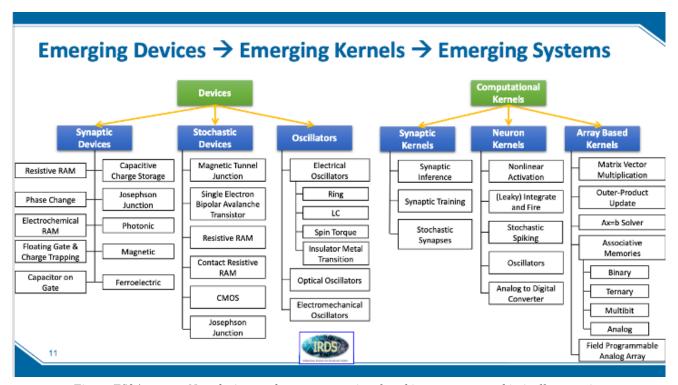

| Figure | ES34 | New devices and new computational architectures are mbiotically emerging                                                                                           |    |

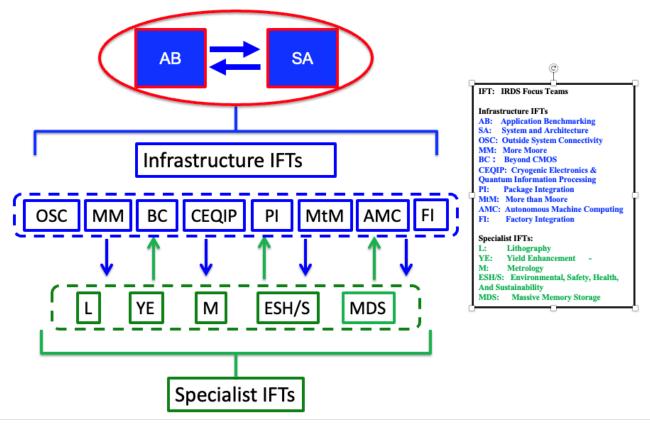

| Figure |      | IFT structure of IRDS                                                                                                                                              |    |

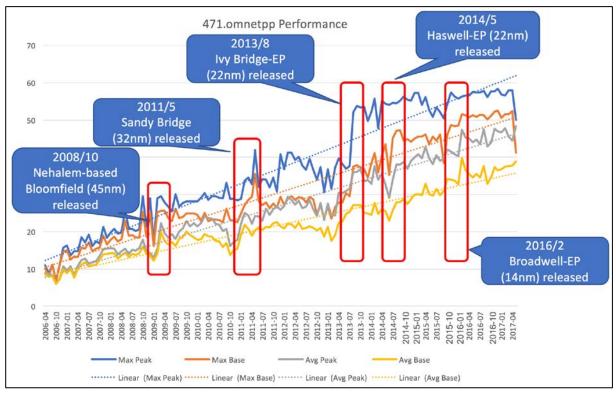

| -      |      | Historical performance over time of 471.omnetpp benchmark                                                                                                          |    |

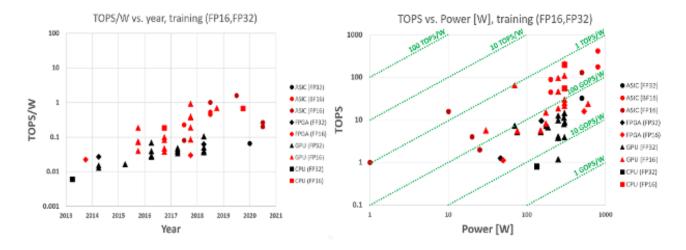

| Figure | th   | TOPS (data points) and the resulting TOPS/W (assessed against e green dotted lines) as a function of reported system power in (a) the aining and (b) the inference | 43 |

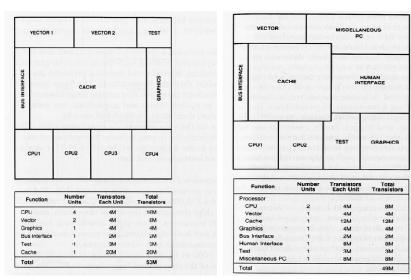

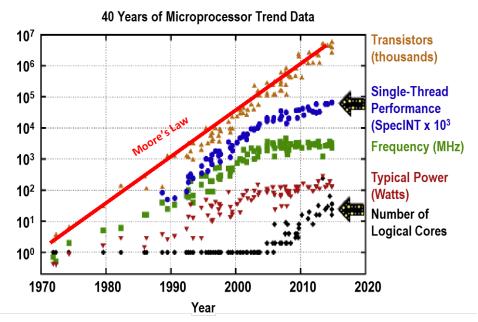

| Figure |      | Prediction of MPU migration multicores outlined in 1989                                                                                                            |    |

| Figure |      | Adoption of multicore architecture allowed moderate performance crease in CPU design within power limits                                                           | 55 |

| Figure |      | Performance resuming and exceeding historical trends by using PU-accelerated computing                                                                             | 56 |

| Figure | ES41 | Trade-off between CPU flexibility and ASIC efficiency                                                                                                              | 57 |

| Figure |      | Performance of computation can be increased by translating repeating of tware instructions into hardware                                                           | 59 |

| Figure |      | Multiple computing operations embedded in hardware and ctivated by software (see color activated specialized computing blocks)                                     | 59 |

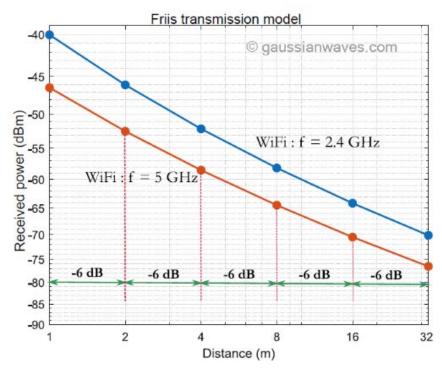

| Figure | ES44 | A. Friis Free Space Equation                                                                                                                                       | 61 |

| Figure | ES44 | B. Example of effect of frequency in reducing propagation radius                                                                                                   | 62 |

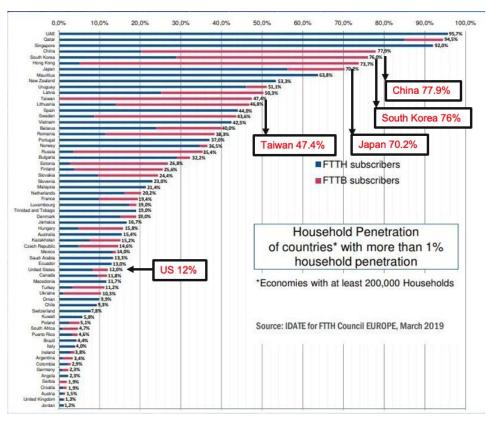

| Figure |      | Household penetration of fiber optics connections for high-speed ommunication                                                                                      | 63 |

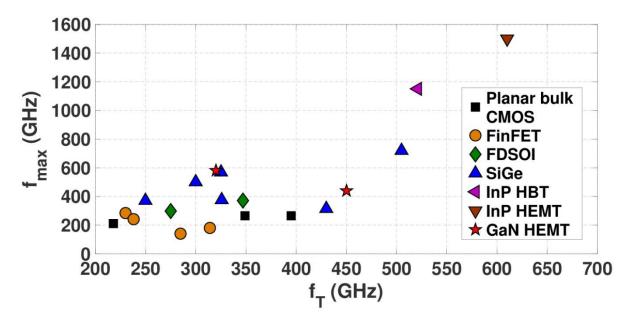

| Figure | ES46 | Silicon device limitations to operate above 400 GHz                                                                                                                | 63 |

|        |      | The multiple aspects computing in the communication world                                                                                                          |    |

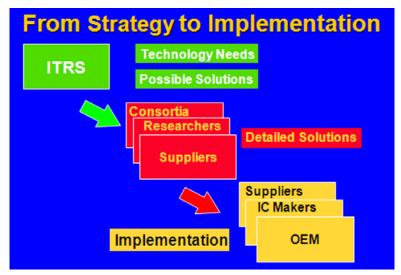

| Figure | ES48 | 1998 ITRS program: from strategy to implementation                                                                                                                 | 66 |

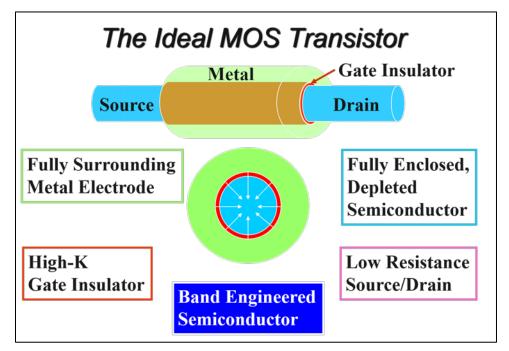

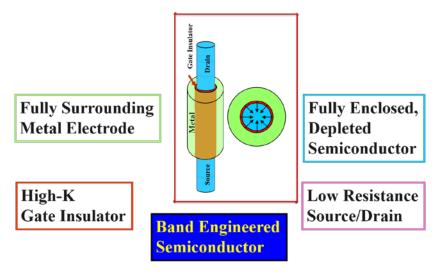

| Figure | ES49 | Vision of the completely refurbished MOS transistor                                                                                                                | 66 |

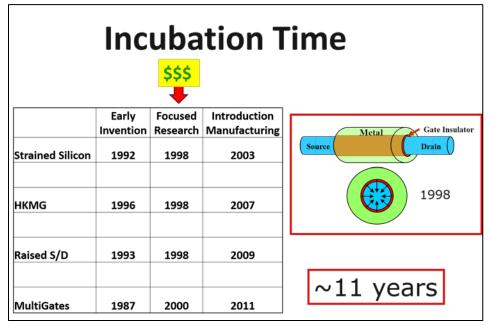

| Figure |      | From strategy to implementation in high-volume manufacturing in ecord time                                                                                         | 67 |

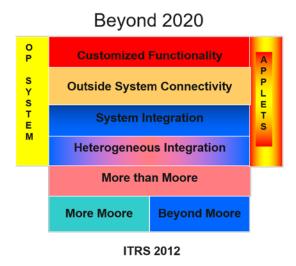

| Figure | ES51 | The new ecosystem of the electronics industry                                                                                                                      | 67 |

| Figure | ES52 | 2D scaling will reach fundamental limits beyond 2020                                                                                                               | 68 |

| _      |      | Flash memory aggressively adopts 3D scaling in 2014                                                                                                                |    |

| •      |      | The ideal 3D transistor                                                                                                                                            |    |

| Figure | ES55 | The 3 eras of scaling heralded by NTRS, ITRS, ITRS 2.0, and IRDS                                                                                                   | 69 |

| Figure ES             | to fully verticalto fully vertical                                                                                | 70 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------|----|

| Figure ES             | 57 Change in the MOSFET device architecture from the 2D planar through 2.5D FinFET to 3D monolithic VLSI with GAA | 70 |

| Figure ES             | 58 Planning for the advent of monolithic heterogeneous integration                                                | 71 |

| Figure ES             | 59 Two complementary ways of increasing transistor and functionality trends                                       | 71 |

| Figure ES             | 60 In the not-too-distant future quantum computing must make some hard device selection                           | 72 |

| List of Tables        |                                                                                                                   |    |

| Table ES1             | Overall Roadmap System Characteristics                                                                            | 44 |

| Table ES2             | System Integration Anchor Points                                                                                  | 45 |

| Table ES3             | Overall Roadmap Technology Characteristics                                                                        | 45 |

| Table ES <sup>2</sup> | Systems and Architectures Technology Trends of Latency Sensitive Processers                                       | 58 |

# **Acknowledgments**

#### **International Roadmap Committee**

Europe—Francis Balestra, Mart Graef

Japan—Yoshihiro Hayashi, Norikatsu Takaura, Hidemi Ishiuchi

U.S.A.— Paolo Gargini-chair, Tom Conte-vice-chair

#### **IEEE**

Rebooting Computing and Standards Association, with special thanks to Erik DeBenedictis, Terence Martinez, Rudi Schubert, William Tonti, and Elie Track

Electron Devices Society—Fernando Guarin and Terence Hook

# The outstanding work by the members of the International Focus Teams is acknowledged in each of their roadmap chapters.

The chairs and co-chairs of these teams are as follows:

Application Benchmarking—Tom Conte

Systems and Architectures—Kirk Bresniker and Stephen Dukes

Outside Systems Connectivity—Michael Garner

More Moore—Mustafa Badaroglu

Lithography—Mark Neisser

Factory Integration—Supika Mashiro and James Moyne

Yield—Slava Libman and Don Wilcox

Beyond CMOS—An Chen, Shamik Das and Matt Marinella

Cryogenic Electronics and Quantum Information Processing—Scott Holmes

Packaging Integration—Dev Gupta

Metrology—George Orji, Ben Bunday, Yaw Obeng

Environment, Safety, Health, and Sustainability—Leo Kenny and Steve Moffat

More than Moore—Mart Graef

Autonomous Machine Computing -Shaoshan Liu and Jean-Luc Gaudiot

Mass Memory Storage - Tom Coughlin and Roger Hoyt

IRDS Project Manager

Linda S. Wilson

Special Acknowledgment

Alan K. Allan

# **IRDS IEEE Societies and Councils Support Organizations**

# Supporting Councils and Societies

# **FOREWORD**

The IEEE International Roadmap for Devices and Systems (IRDS) is the continuation and extension of the National Technology Roadmap for Semiconductors/International Technology Roadmap for Semiconductors (NTRS/ITRS) with a record of uninterrupted publications spanning from 1992 to 2015. The IRDS has followed several of the successful methodologies demonstrated by the NTRS/ITRS with additional expansion to system integration, data centers and Internet communications requirements as well as quantum computing and quantum communications. The IRDS has been previously published in 2016, 2017, 2018, 2020 and 2021.

Historically the draft of all the chapters of the ITRS used to be collected in the month of October. Afterwards, the Executive Summary was quickly assembled and delivered to the Semiconductor Industry Association (SIA) Board at their mid-November annual meeting.

In the subsequent months major results and forecasts for the following year were delivered in key conferences like the International Electron Devices Meeting (IEDM) (mid-December) and International Solid-State Circuits Conference (ISSCC) (late-February). In addition, multiple company announcements were made in January outlining their vision for the year that had just started. Historically, the publication of ITRS was timed consistently with the SIA board meeting. With the transition to IEEE in May 2016 this constraint no longer existed, and the publication schedule evolved towards release of the IRDS at the beginning of 2Q of the following year. As a result, all the information that previously was included as part of the roadmap update and scheduled to be published the following year has now become available for the IRDS publication in real time. As a result, the 2019 IRDS was renamed the 2020 IRDS.

Additionally, historically the NTRS/ITRS and IRDS have predicted specific problems to occur early on, allowing enough time for research and supplier organizations to develop possible solutions. For instance, in 1998 the transformation of the planar silicon gate CMOS to strained silicon, high-κ/metal-gate and FinFET was clearly articulated, and these key milestones were accomplished in 2003, 2007 and 2011, respectively. Starting with the 2020 IRDS a section dedicated to Industry Highlights and IRDS messages was introduced to better show the relations between the two organizations.

# **OVERVIEW**

# 1. Introduction

## **IRDS Mission**

Identify the roadmap of electronic industry from devices to systems and from systems to devices.

#### IRDS STRUCTURE

This initiative focuses on an International Roadmap for Devices and Systems (IRDS) through the work of International Focus Teams (IFT) closely aligned with the advancement of the devices and systems industries. Led by the International Roadmap Committee (IRC), IFTs collaborated in the development of the 2022 IRDS roadmap, and engaged with other segments of the IEEE, such as the Rebooting Computing Initiative (RCI), Electron Devices Society (EDS), Computer Society (CS), Communication Society (ComSoc), and other societies as well as with related industry and academic communities like the System and Device Roadmap Committee of Japan (SDRJ) and the European SINANO Institute (ESI) in complementary activities to help ensure alignment and consensus across a range of stakeholders, such as:

- Academia

- Consortia

- Industry

- National laboratories

IEEE, the world's largest technical professional organization dedicated to advancing technology for humanity, through the IEEE Standards Association (IEEE-SA) Industry Connections (IC) program, supports the IRDS to ensure alignment and consensus across a range of stakeholders to identify trends and develop the roadmap for all the related technologies in the computer industry.

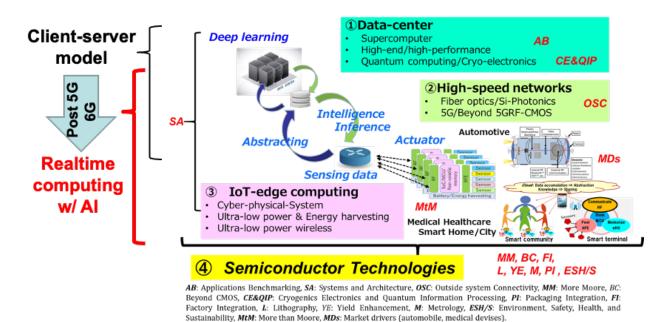

The scope of the IRDS<sup>TM</sup> of the fundamental building blocks in the electronics industry spanning from devices to systems and from systems to devices, in which the AI-centric IoT-social-infrastructures with high-speed network communication will be built on the semiconductor device and process technologies, as illustrated in Figure ES1.

For the 2022 IRDS the Focus Teams are as follows:

- 1. Application Benchmarking (AB) (Same as 2021)

- 2. Systems and Architectures (SA)

- 3. Outside System Connectivity (OSC)

- 4. More Moore (MM)

- 5. Beyond CMOS (BC)

- 6. Cryogenic Electronics and Quantum Information Processing (CEQIP)

- 7. Packaging Integration (PI) white paper (same as 2021)

- 8. Factory Integration (FI)

- 9. Lithography (L)

- 10. Yield Enhancement (YE)

- 11. Metrology (M)

- 12. More than Moore (MtM) white paper

- 13. Environment, Safety, Health, and Sustainability (ESH/S)

Two additional chapters are in the formation stage and white papers are in preparation for the 2022IRDS. Full chapters are expected with the 2023IRDS. These are:

- 14. Mass Data Storage and Non-volatile Memory

- 15. Autonomous Machine Computing

White papers for these new focus areas will be part of the 2022 IRDS.

Each of the IFTs are focusing not only on technical roadmaps in their specific areas but also on cross-boundary areas among the systems and the devices, or the devices and the fabrication process technologies. The major revision of the IRDS roadmaps is updated every two years, while minor revisions are done every year if necessary. Here, the IRDS 2022 Edition is the material resulting from revisions to the 2021 IRDS. Under management of the international roadmap committee (IRC) of the international representatives, the technical points in each IFT have been selected and discussed internally, and the results are being released to public through the IEEE IRDS homepage (irds.ieee.org).

Figure ES1 IRDS Scope

The scope of the  $IRDS^{\mathbb{N}}$  of the fundamental building blocks in the electronics industry spanning from devices to systems and from systems to devices under the international collaboration to discuss the focus points. See the details in Section 2.1, "Roadmap Process".

The new ecosystem of the electronics' industry based on semiconductor technologies.

#### **IEEE Sponsors**

The IRDS is sponsored by the IEEE Rebooting Computing (IEEE RC) Initiative in consultation and support from many IEEE Operating Units and Partner organizations, including the following:

CASS—Circuits and Systems Society

CEDA—Council on Electronic Design Automation

CS—Computer Society

CSC—Council on Superconductivity

**EDS**—Electron Devices Society

**EPS**— Electronics Packaging Society

MAG—Magnetics Society

NTC—Nanotechnology Council

PELS—Power Electronics Society

RS—Reliability Society

SSCS—Solid State Circuits Society

SRC—Semiconductor Research Corporation

**IEEE Standards Association**

### INTERNATIONAL SPONSORS AND COOPERATION

There are several international roadmap efforts directly aligned with the IRDS:

- The SINANO Institute http://www.sinano.eu/

- The System Device Roadmap Committee of Japan (SDRJ) https://www.sdrj.jp/

- The International Electronics Manufacturing Initiative (iNEMI) http://www.inemi.org/

# 1.1. 2021/2022 INDUSTRY HIGHLIGHTS AND KEY MESSAGES FROM THE 2022 IRDS

The events of 2020 and 2021 were very dramatic as the whole world was overwhelmed by the first pandemic in 100 years. However, the need to remotely communicate, acquire goods, handling banking and business transactions accelerated several aspects of the electronics industry. It would have probably taken more than five years under normal conditions to more organically proliferate so many technologies. In addition, new customers that had not expected to even become acquainted with some of these technologies (e.g., notebooks, zoom communications, on-line purchasing, etc.) were compelled to become familiar with these new technologies.

This Executive Summary will highlight the progress made in 2021 and forecast some of the trends in 2022 and beyond. There are many subjects that could be addressed to place the 2022 IRDS in contest but this is a simple collection of few key items to be brought to the attention of the reader.

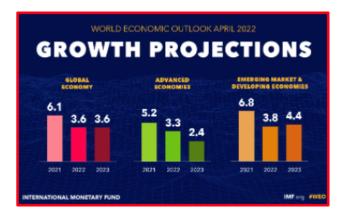

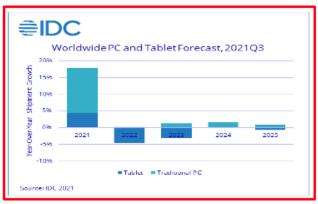

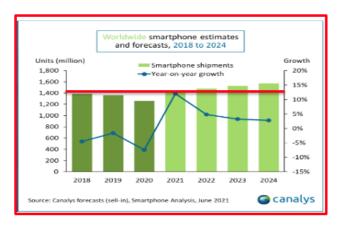

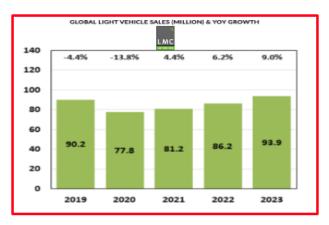

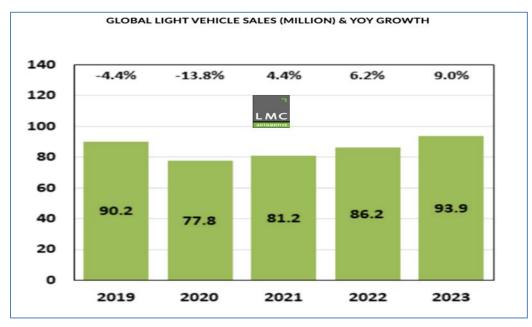

The global GDP surged in 2021 as compared to a decline in 2020 as industry began to learn how to deal with the problems induced by the pandemic. A good but moderate 3.6% GDP growth is expected to follow in 2022 as well (barring exceptional uncontrollable events *that may reduce it even further*) as more businesses continue to resolve their suppliers' chain issues. The electronic industry remained very healthy in 2021; for instance, smartphones units grew 5.5.% in 2021 and units are expected to continue growing 3.7% in 2022. This contrast with declines in both 2019 and 2020. PC units grew an unexpected 13% in 2020 and 18% in 2021 due to the necessity for consumers and employees to remotely communicate during the pandemic. This trend is expected to decline in 2022 but at a level 26% higher than 2019 according to multiple reports. As a result, both the sales of electronics systems and the number of IC units are expected to continue growing in 2022 as compared to 2020. It is also evident that despite reports the automobile industry is back in full force. See Figure ES2.

# **Key Semiconductor Drivers Forecasts**

|                |                   | <u>2019</u>    | 2020           | 2021          | 2022          | 2022           |                        |

|----------------|-------------------|----------------|----------------|---------------|---------------|----------------|------------------------|

| Global GDP     | Change            | 2.8%           | -3.3%          | 6.0%          | 4.4%          | 3.6%           | Original<br>Forecast   |

| Smartphones    | M units<br>Change | 1,373<br>-2.3% | 1,280<br>-6.7% | 1,350<br>5.5% | 1,400<br>3.7% | 1,400+<br>3.7% |                        |

| PCs            | M units<br>Change | 268<br>3%      | 302<br>13%     | 357<br>18%    | 340<br>-5%    | 340<br>-5%     | Forecast<br>April 2022 |

| Light vehicles | M Units<br>Change | 89<br>-4%      | 76<br>-15%     | 81<br>5%      | 86<br>6%      | 86<br>6%       |                        |

Source: Compiled reports

Figure ES2 A. Compilation of relevant trends associated with the electronics industry

Figure ES2 B. Forecasted GDP, Smartphones, PC and Light Vehicle trends

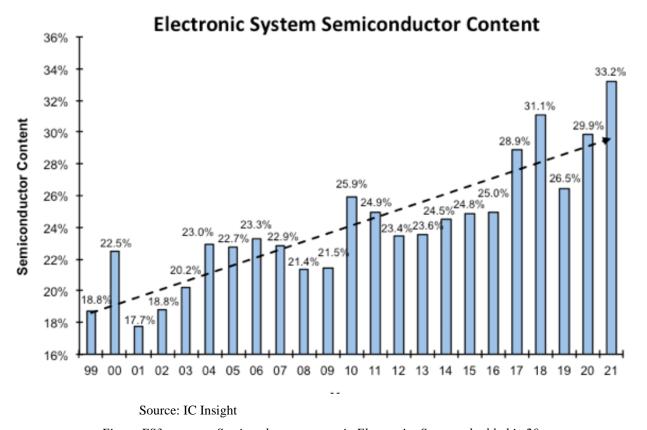

Semiconductor content in electronic system took a 3% upward jump in 2021 as pervasive adoption of semiconductors in all the devices surrounding any aspect of society continued. Semiconductors have become a vital part of any system. As an example, most of any mechanically operating parts are no longer manually or mechanically actuated but are instead

controlled via integrated circuits. Figure ES3 shows that in the past 20 years the semiconductor content in electronics systems has doubled. It is expected that this trend will continue for the foreseeable future. See Figure ES3.

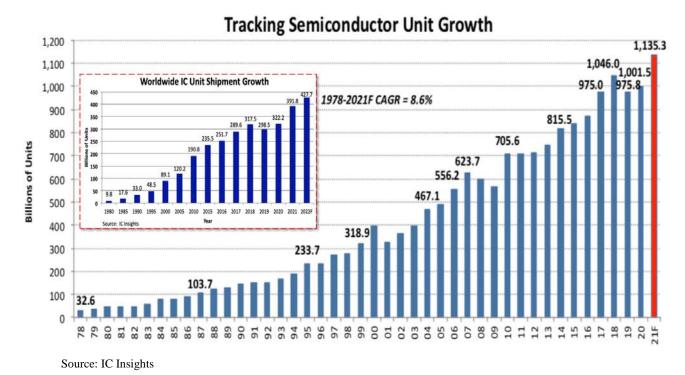

Figure ES3 Semiconductor content in Electronics Systems doubled in 20 years

After a slight decline in 2019 and 2020 the number of units shipped in 2021 resumed trending up, exceeding the 1.1 billion units mark for the first time. More relevant is the fact that IC unit shipments were just shy of 400 billion. The huge 22% increase in IC units in the year 2021 from the year 2020 brings the growth rate of IC unit shipments back in line with the historical 8.6% CAGR established as far back as the late 70s. This is another sign indicating that semiconductor components remain the foundation of the electronics industry.

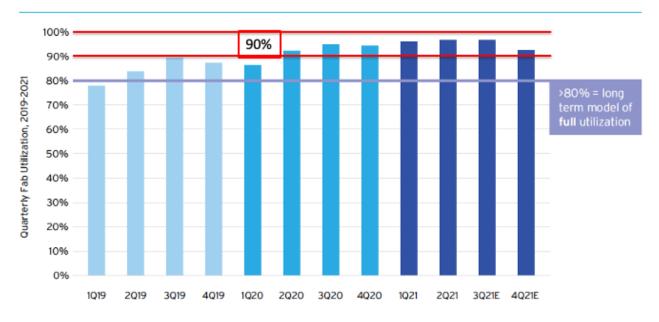

The pandemic had initially a strong effect on the semiconductor industry in 1Q, 2020 but in response manufacturing output was increased by 3Q 2020 by boosting up fab utilizations from the mid-80% to the mid 90%. As a result, most shortages of semiconductors were practically eliminated by 2H 2021. See Figure ES4.

Figure ES4 Growth of units resumes at the historical rate of 8.4%CAGR

Supply chain issues severely impacted shipments of semiconductors in 1Q2020. Semiconductor manufactures aggressively raised factory utilization to unprecedented levels beginning with 2Q2020 and have continued at this pace to this date. This effort is reflected in the resumed growth of units and revenue to record levels in 2021.

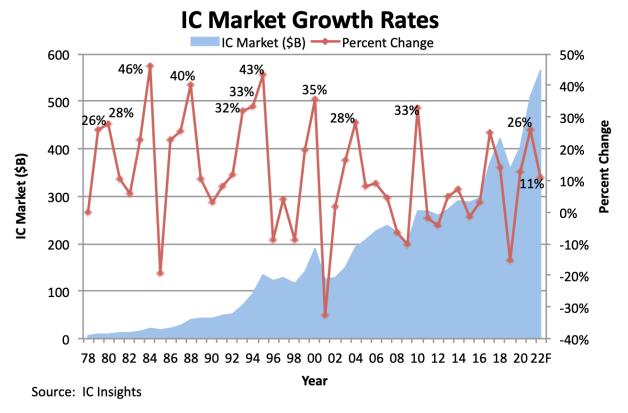

Users of semiconductors placed an exuberant number of orders to make up for the lost deliveries in 2020 and to accumulate reserves for 2022-2023, protecting them against any possible reoccurrence of any shortages due to unforeseen circumstances due to the complex and unprecedented events occurring in 2022 around the world. On the other hand, multiple semiconductor manufacturers became very anxious to resume or exceed the growth experienced in 2021 and even more so to exceed historical growth rates in 2022-2023. Given the predominate role demonstrated by semiconductor components on the world economy, these circumstances have led to a surge in capital investments well beyond historical trend. Similar euphoria in capital investments have resulted in a semiconductors glut following a shortage with consequent collapse in selling prices in the past. Will the electronic industry be able to absorb in a timely fashion this wave of semiconductor products? Stay tuned. (See Figure ES6)

# 2016-2022F IC Industry Capacity Trends (200mm Equivalents)

| Year  | Total IC<br>Wafer<br>Capacity (M) | IC Wafer<br>Capacity<br>% Chg | Total IC<br>Wafer Starts<br>(M) | IC Wafer<br>Starts<br>% Chg | Total IC<br>Capacity<br>Utilization |

|-------|-----------------------------------|-------------------------------|---------------------------------|-----------------------------|-------------------------------------|

| 2016  | 178.9                             | 4.0%                          | 161.5                           | 4.9%                        | 90.3%                               |

| 2017  | 190.5                             | 6.5%                          | 175.8                           | 8.9%                        | 32.3%                               |

| 2018  | 201.6                             | 5.8%                          | 188.9                           | 7.5%                        | 93.7%                               |

| 2019  | 209.8                             | 4.1%                          | 180.0                           | -4.7%                       | 85.8%                               |

| 2020  | 223.5                             | 6.5%                          | 191.1                           | 6.2%                        | 85.5%                               |

| 2021  | 242.5                             | 8.5%                          | 227.5                           | 19.0%                       | 93.8%                               |

| 2022F | 263.6                             | 8.7%                          | 245.1                           | 7.7%                        | 93.0%                               |

Source: IC Insights, Knometa Research, WSTS, SIA

Figure ES6 IC wafer capacity growing above 8% yearly rate in 2021 and 2022

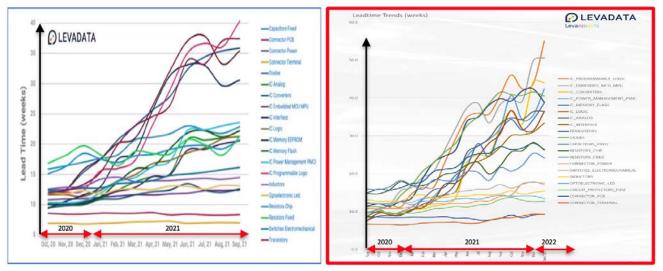

The Pandemic strongly affected shipments of motor vehicle due to chip shortages in 2020. Most of these problems have been resolved. However, even though some selective problems with the supply chain still exist (e.g., capacitors, diodes

etc.) the shipment of motor vehicles resumed at a very strong rate in 2021 due to the enhancement of shipments supported by factory utilization approaching 95% at most semiconductor manufacturing facilities. (See Figures 7A and 7B)

Figure ES7 A. While semiconductor delivers recovered many other items are still experiencing major delays in the supply chain

Figure ES7 B. Shipments of motor vehicle approaching getting back on track

Overall IC sales passed for the first time the \$500B revenue mark growing 26% in 2021. A still healthy 11% growth is anticipated for 2022. The major risk for the semiconductor industry is now constituted by a possible oversupply looming in the not-too-distant future that may repeat the glut problems seen in the 2002 and 2007-9 timeframes before. See Figure ES8.

Figure ES8 Semiconductor forecasted growth may swing from exuberance to collapse

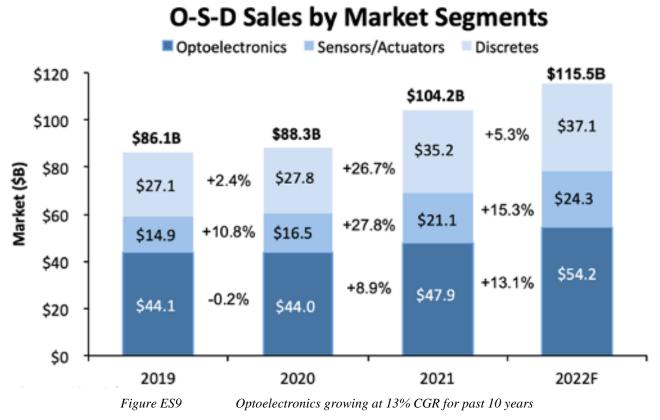

Video sensors that use optoelectronics and are connected to the internet have strongly contributed to the increase in internet usage and vice versa. For the first time, optoelectronic, sensor/actuator, discrete (OSD) sales crossed the \$100B level in 2021. Sensors and actuators sales grew 26% in 2021. The solidity of this trend is further demonstrated by the fact

that worldwide sales of these components doubled from 2011 to 2021. The overall OSD sales trend is expected to continue growing at 11% level in 2022. See Figure ES9.

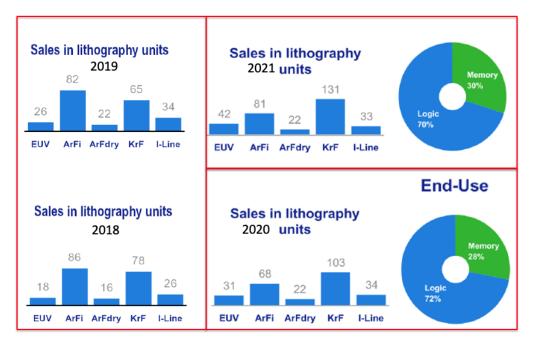

Shipments of EUV lithography systems grew 31% in 2021 driven by fast adoption rate of this technology by logic companies. EUV lithography represents an attractive way of reducing the numbers of masking layers requiring multiple exposures using 193 nm immersion tools. EUV technology is probably holding the incubation record from prototype to commercial unit. It took the longest time to be implemented spanning from inception in 1996; realization of the first demonstration tool (Engineering Test Stand, ETS) sponsored by the EUV Limited Liability Corporation (EUVLLC) in 2001; first two research prototypes delivered in 2006; source acquisition in 2012, and finally shipment of the first 11 manufacturing units in 2017. Altogether 128 EUV units have been sold since 2017. Present EUV tools feature a lens numerical aperture (nA) of 0.33; however, this is not the end as design of a 0.55 NA tool is in progress. See Figure ES10.

Source: ASML, 2018-2022, Earning reports

Figure ES10 Shipments of EUV lithography scanners continued to grow in 2021

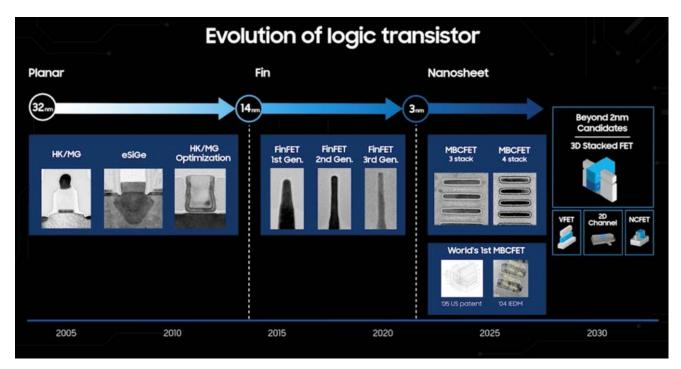

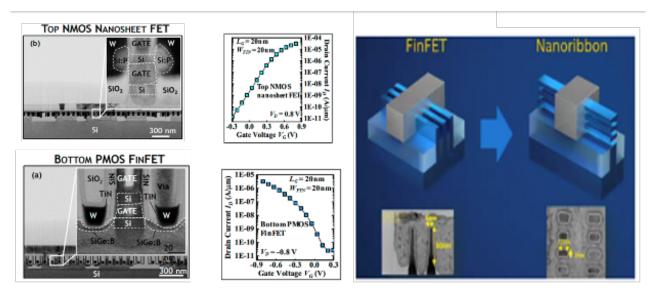

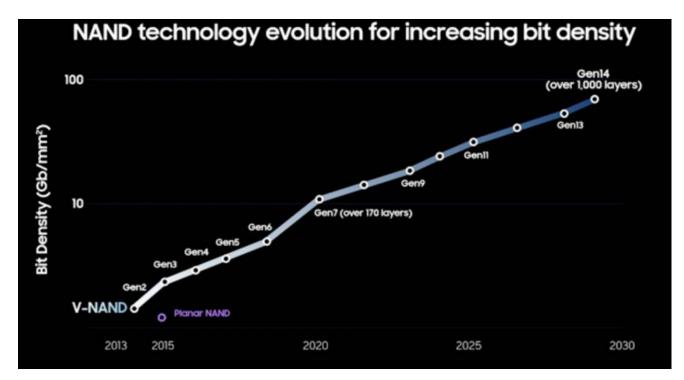

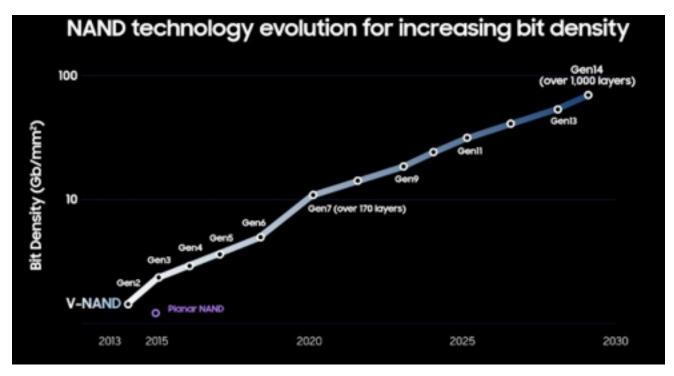

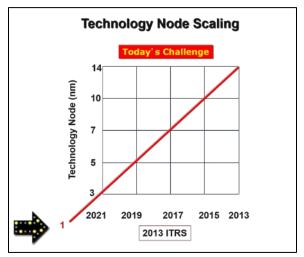

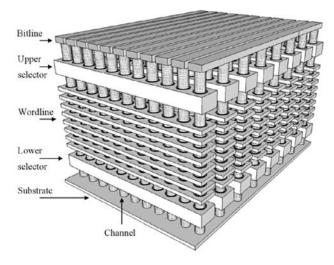

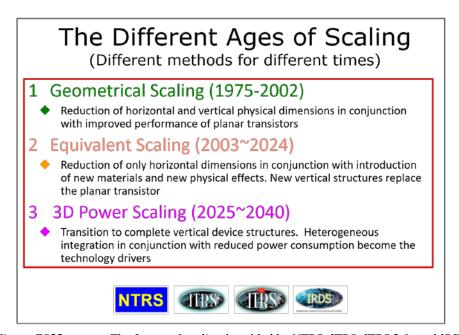

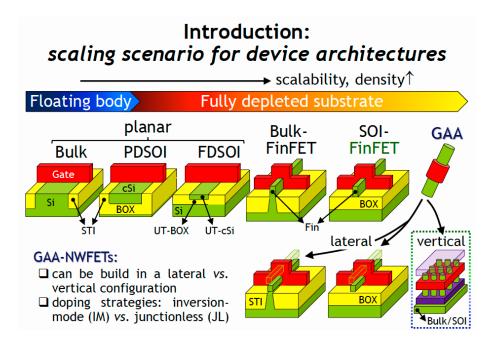

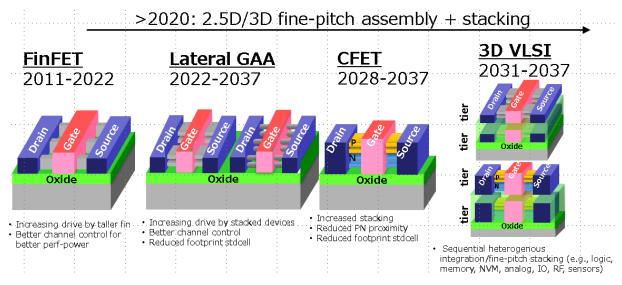

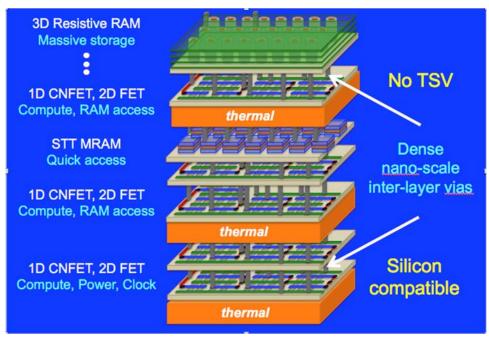

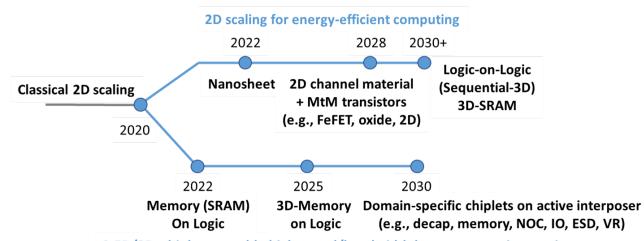

Overall industry technology progression remained consistent with the 2020-2022 IRDS forecasts. Half metal pitch (the one and only indicator of technology node since inception of the roadmap process in the early 90s) reached the 15 nm mark last year and it is anticipated to reach 12 nm this year. EUV technology will support the continuation of metal half-pitch scaling well until around 8 nm by the end of this decade. As previously anticipated transition to gate all around (GAA) transistor for logic is on track for 2025. This date will mark the last step in the transition to full 3D device architecture for logic following the similar transition that occurred in 2015 for Flash memory, a prediction by the 2013 ITRS. Today Flash products are packing close to 200 memory-cell layers in manufacturing. See Figures ES11A-E.

| YEAR OF PRODUCTION                                    | 2022     | 2025     | 2028              | 2031                    | 2034                    | 2037                    |

|-------------------------------------------------------|----------|----------|-------------------|-------------------------|-------------------------|-------------------------|

|                                                       | G48M24   | G45M20   | G42M16            | G40M16 T2               | G38M16 T4               | G38M16 T6               |

| Logic industry "Node Range" Labeling                  | "3nm"    | "2nm"    | "1.5nm"           | "4.0nm eq"              | "0.7nm eq"              | "0.5nm eq"              |

| Fine-pitch 3D integration scheme                      | Stacking | Stacking | Stacking          | 3DVLSI                  | 3DVLSI                  | 3DVLSI                  |

|                                                       | finFET   |          | LGAA              | LGAA-3D                 | LGAA-3D                 | LGAA-3D                 |

| Logic device structure options                        | LGAA     | LGAA     | CFET-SRAM         | CFET-SRAM               | CFET-SRAM               | CFET-SRAM               |

| Platform device for logic                             | finFET   | LGAA     | LGAA<br>CFET-SRAM | LGAA-3D<br>CFET-SRAM-3D | LGAA-3D<br>CFET-SRAM-3D | LGAA-3D<br>CFET-SRAM-3D |

|                                                       |          |          |                   | tier tier tier tier     | owe der der der         | der der der der         |

| LOGIC DEVICE GROUND RULES                             | 2        |          |                   | -                       |                         |                         |

| Mx pitch (nm)                                         | 32       | 24       | 20                | 16                      | 16                      | 16                      |

| M1 pitch (nm)                                         | 32       | 23       | 21                | 20                      | 19                      | 19                      |

| MO pitch (nm)                                         | 24       | 20       | 16                | 16                      | 16                      | 16                      |

| Gate pitch (nm)                                       | 48       | 45       | 42                | 40                      | 38                      | 38                      |

| Lg: Gate Length - HP (nm)                             | 16       | 14       | 12                | 12                      | 12                      | 12                      |

| Lg: Gate Length - HD (nm)                             | 18       | 14       | 12                | 12                      | 12                      | 12                      |

| Channel overlap ratio - two-sided                     | 0.20     | 0.20     | 0.20              | 0.20                    | 0.20                    | 0.20                    |

| Spacer width (nm)                                     | 6        | 6        | 5                 | - 6                     | 4                       | 4                       |

| Spacer k value                                        | 3.5      | 3.3      | 3.0               | 3.0                     | 2.7                     | 2.7                     |

| Contact CD (nm) - finFET, LGAA                        | 20       | 19       | 20                | 18                      | 18                      | 18                      |

| Device architecture key ground rules                  |          |          |                   |                         | 77.5                    |                         |

| Device lateral pitch (nm)                             | 24       | 26       | 24                | 24                      | 23                      | 23                      |

| Device height (nm)                                    | 48       | 52       | 48                | 64                      | 60                      | 56                      |

| FinFET Fin width (nm)                                 | 5.0      |          |                   | - 111                   |                         |                         |

| Footprint drive efficiency - finFET                   | 4.21     |          |                   |                         |                         |                         |

| Lateral GAA vertical pitch (nm)                       |          | 18.0     | 16.0              | 16.0                    | 15.0                    | 14.0                    |

| Lateral GAA (nanosheet) thickness (nm)                |          | 6.0      | 6.0               | 6.0                     | 5.0                     | 4.0                     |

| Number of vertically stacked nanosheets on one device |          | 3        | 3                 | 4                       | 4                       | 4                       |

| LGAA width (nm) - HP                                  |          | 30       | 30                | 20                      | 15                      | 15                      |

| LGAA width (nm) - HD                                  |          | 15       | 10                | 10                      | 6                       | 6                       |

| LGAA width (nm) - SRAM                                |          | 7        | 6                 | 6                       | 6                       | 6                       |

| Footprint drive efficiency - lateral GAA - HP         |          | 4.41     | 4.50              | 5.47                    | 5.00                    | 4.75                    |

| Device effective width (nm) - HP                      | 101.0    | 216.0    | 216.0             | 208.0                   | 160.0                   | 152.0                   |

| Device effective width (nm) - HD                      | 101.0    | 126.0    | 96.0              | 128.0                   | 88.0                    | 80.0                    |

| PN seperation width (nm)                              | 45       | 40       | 20                | 15                      | 15                      | 10                      |

Figure ES11 A. Devices will continue to aggressively scale in the next five years. Logic transition to 3D is still aimed at 2025

Figure ES11 B. Transitions from 2D to 3D device architecture in NAND and Logic is progressing as predicted by 2013 ITRS

Source: Intel investor meeting 2022

Figure ES11 C. Transistor 2003-2025 evolution: From 2D Equivalent scaling to 3D Power scaling

Source: IMEC and Intel

Figure ES11 D. Vertical transistors and nanoribbons are progressively entering the logic technology arsenal

Source: Samsung

Figure ES11 E. 3D NAND evolution: from 32 layers in 2025 to over 1000 layers by 2030

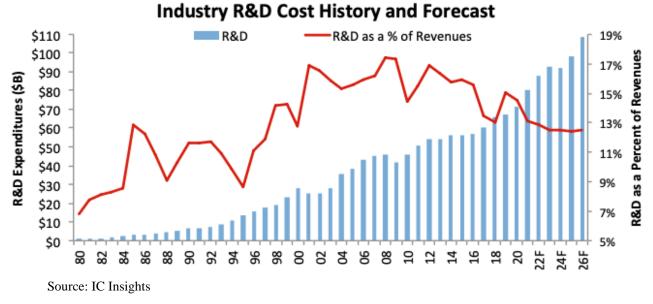

R&D spending drastically increased above a dangerous level of 15% of revenue between the years 2000 and 2011 as the semiconductor industry was undergoing the transition from 200 mm to 300 mm wafers size in manufacturing. In addition, the introduction of revolutionary technologies like strained silicon, high-κ/metal-gate and fin field-effect transistor (FinFET) pushed the R&D budget of most companies into dangerously high levels. However, between 2011 and 2014 all these major transitions were completed. Despite the rise in technology complexity (mostly due to increases in the number of process steps—especially the fast-rising number of masks—rather than to the introduction of new and expensive revolutionary technologies) R&D spending has continues to decline. Lately, the transition to EUV is actually keeping

R&D spending well below 15% of revenue (mostly due to the drastic reduction in the number of multiple masks/layer into a single one). This trend is expected to continue for at least the next 4-5 years. See Figure ES12.

Figure ES12 R&D spending remains under control

The rate of introduction of new Logic technologies by TSMC and Samsung has accelerated in the past four years. The introduction of EUV lithography is expected to continue supporting this accelerated trend. See Figure ES13.

#### 2016 2017 2018 2019 2020 2021 2022 10<sub>nm</sub> 7nm EUV Intel 14nm+ 10nm 10nm+ 10nm++ 14nm++ 7nm EUV 18nm 3nm GAA 10nm 8nm Samsung 4nm 6nm 5nm 7<sub>nm</sub> 7nm+ **TSMC** 10<sub>nm</sub> 5nm+ 6nm 3nm 12nm 22nm+ FDSOI 12nm+ finFET 12nm FDSOI 22nm 12nm FDSOI finFET GlobalFoundries 8-10nm 14nm 12nm **SMIC**

# Logic/Foundry Process Roadmaps (for Volume Production)

Note: What defines a process "generation" and the start of "volume" production varies from company to company, and may be influenced by marketing embelishments, so these points of transition should only be seen as very general guidelines.

22nm

Sources: Companies, conference reports and IC Insights

UMC

14nm

Figure ES13 Scaling progressing unabated with EUV technology

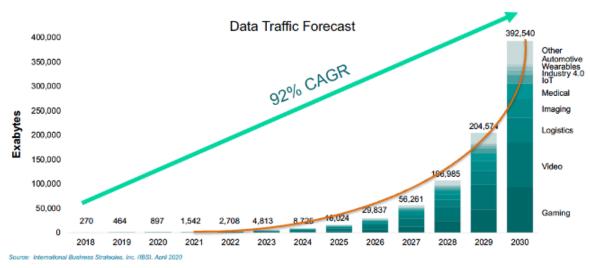

Early on, the Internet fostered widespread use of email communications and then blossomed into pictures, videos, movies, and data streaming. However, the most relevant indicator of internet proliferation can be seen by observing the trend in the rate of adoption in the business world. The result of the proliferations and wide diffusion of these capabilities among industry and consumers is increasing the demand for higher data rates. It is expected that the rate will double from 2018 to 2030. (See Figure ES14).

# Exponential data traffic, enabled by machine-to-machine communication

Source: International Business Strategies, Inc.

Figure ES14 Communication traffic growing close to doubling every year for the foreseeable future

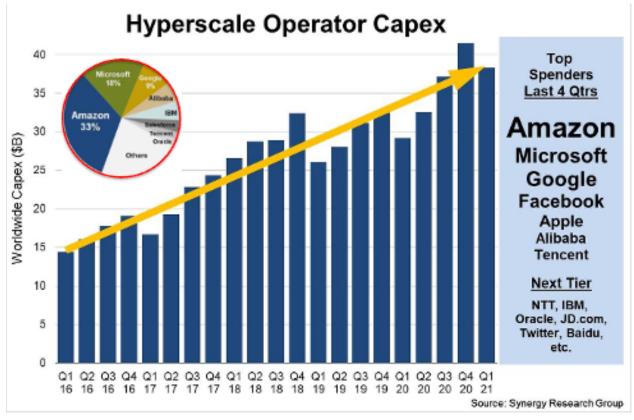

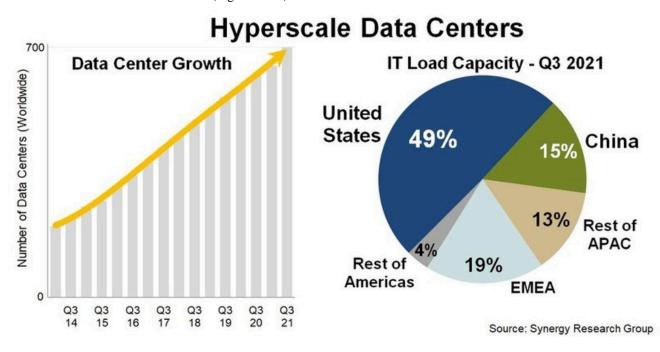

Hyperscale data centers continue to remain the repository of information for the Internet. Investments have more than double in the past five years. See Figure ES15.

Figure ES15 Rate of investment in hyperdata centers doubled in 5 years

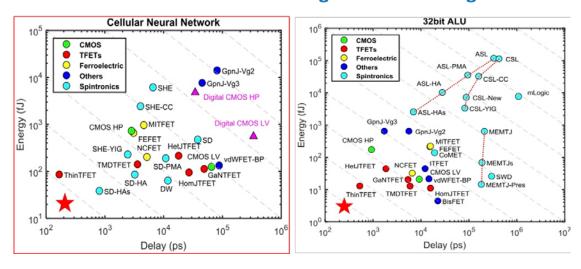

Research in Beyond CMOS devices continues to successfully proceed. Performance of several new devices is continuing to improve. See Figure ES16. (Refer to the 2022 Beyond CMOS Chapter for more information.)

# **TFET Performance is Moving Close to the Target!**

Figure ES16 Performance of devices beyond CMOS continues to improve towards goal

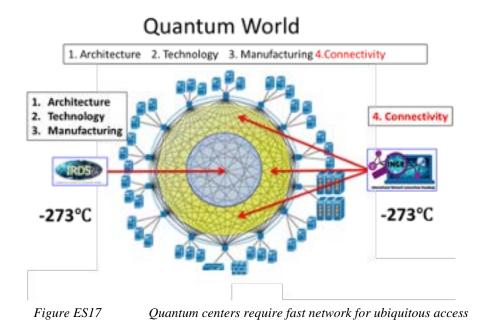

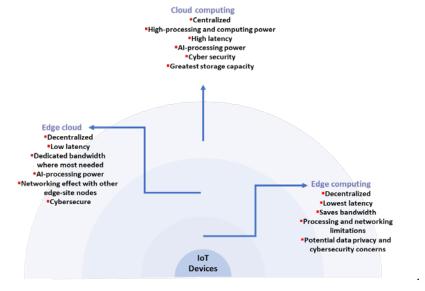

Most of the more promising implementations of quantum computing (QC) operate at temperatures as low as -273°C. Due to this constraint consumers will not be able to carry QC mobile devices in their pockets and will have to rely on powerful and far-reaching 5G/6G networks to remotely access data centers for information and quantum centers for computing. This vision for the year 2030 and beyond is supported by IRDS and the IEEE International Network Generations Roadmap (INGR). See Figure ES17.

## 1.2. THE NEW ECOSYSTEM OF THE ELECTRONICS' INDUSTRY

# 1.2.1. THE BIG PICTURE

The **computer industry** and the semiconductor industry together have been driving the growth of the electronics industry for over 60 years. This combination has produced faster, smaller, and cheaper components that have enabled progressively larger, faster, and more powerful computing machines. Close cooperation with leaders in the software industry simplified and solidified the association between hardware and software. The introduction of the personal computer (PC) to corporations in the 80s was closely followed by the diffusion of PCs and notebooks to consumers in the 90s; these appliances were capable of doing computation and were also capable of connecting to the Internet by means of somewhat awkward cables. Introduction of Wi-Fi in 1998 operating at 2.4 GHz eliminated this problem and increased employees' productivity by making the connection to the Internet completely ubiquitous and almost instantaneous inside corporations. On the other hand, by then the consumers were already dependent on cell phones and were ready for more. Since then, a new operating frequency of 5 GHz was introduced in 2009 (802.11ac). Next, Wi-Fi6 (802.11ax) operating in the range 5.925 GHz and 7.125 GHz was introduced in 2021. Data transfer rates as high as 9.6 Gbit/sec are possible with Wi-Fi6.<sup>1</sup>

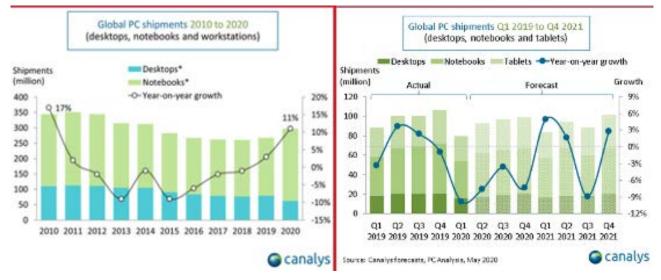

Cell phones and Wi-Fi notebooks had already created the working attitude of "business on the go" especially in the business community but consumers were also closely following in the adoption of mobile devices. Meanwhile, the size of the electronics inside a cell phone kept on reducing, driven by Moore's Law and from the 2" by 5" size of typical cell phones in the 90s new cell phones that had reduced in form factor to a 1" by 2" format in early 2000. It may seem obvious looking back now but this implied that there was a lot of space potentially available to fill up the early cell phone format with a lot of electronics, and in 2007, the iPhone did just that. Now a single device could provide everything that consumers had done with PCs, notebooks, cell phones, video players and even more (books, songs, pictures and more). Sales of PCs and notebooks had been declining since 2011. However, the pandemic has seen a multitude of new users reversing this trend as they were compelled to use some form of personal computer in 2020 as a means of communication and personal computer sales soared 11% in 2020. A similar trend

,

<sup>1</sup> https://standards.ieee.org/ieee/802.11ac/4473/

was seen in 2021 and sales grew 18%. See Figure ES18. However, it is expected that in 2022 the growth rate will decline by 5%. See Figure ES2.

Source: Canalys estimates (sell-in shipments, PC Analysis, January 2021

Figure ES18 Pandemic spurred PC sales in 2020-2021!

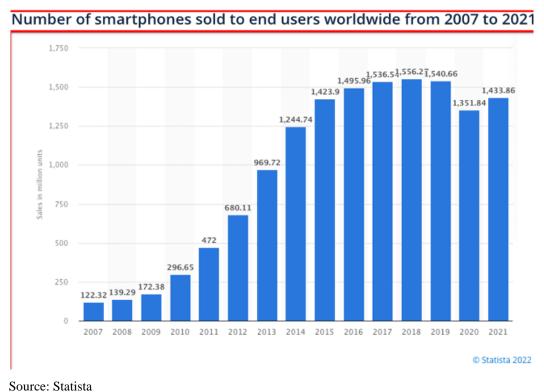

On the other hand sales of smart phones skyrocketed from about 122 million in 2007 (year of introduction) to 1.5 billion units in 2017 and maintained this unit sale level in subsequent years . Sales substantially declined for the first time in 2020 but partially recovered in 2021. (See Figure ES19.)

Figure ES19 Sales of smartphones declined in 2020

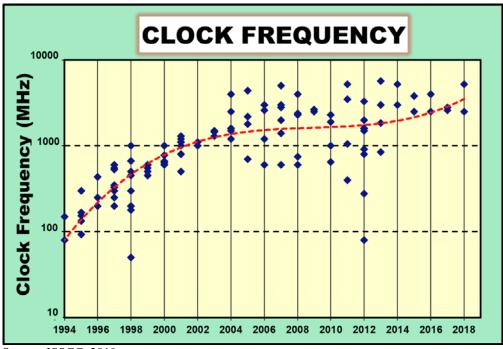

In addition, the power dissipation of microprocessors reached the 120-130 W limits by the middle of the previous decade; however, changing the architecture from a single core to multiple cores operating in parallel alleviated the problem. Despite this architectural transformation the maximum frequency of operation had to be limited to a maximum value less than 10GHz (Figure ES20) to avoid operational problems due to excessive power dissipation (See Section 5 for more details).

Source: ISSCC, 2019

Figure ES20 Clock frequency limited to less than 10GHz by power wall

For the next few years, some level of improvement in computing performance was achieved by implementing the multicore architecture but intrinsically a microprocessor operates by alternating between serial and parallel operations. As a results performance could no longer doubled every two years following historical trends. Since it was becoming evident that it was impossible to completely adapt microprocessor operation to a 100% parallel approach it was then time to turn the table around and ask the question of whether it was possible to find an application that was intrinsically 100% parallel in nature. This concept was quickly reconnected with a type of architecture proposed in 1980 called neuromorphic computing. This architecture proposed the use of very-large-scale integration (VLSI) systems containing electronic analog circuits to mimic neuro-biological architectures present in the nervous system. A key aspect of neuromorphic engineering is understanding how the morphology of individual neurons, circuits, applications, and overall architectures creates desirable computations; affects how information is represented; influences robustness to damage; incorporates learning and development; how it adapts to local change (plasticity) and facilitates evolutionary changes. As an example, oxide-based memristors, spintronics memories, threshold switches, and transistors can easily realize the hardware implementation of neuromorphic computing. It was now a time to answer the question of which application could be best matched to this architecture.

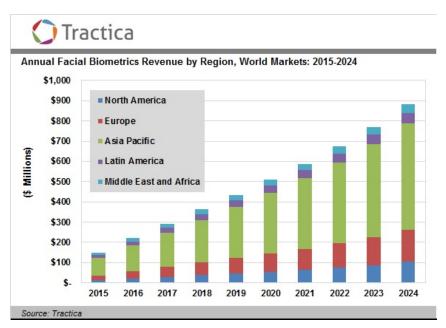

Finally, the right example arrived. In 2007 the ability of systems to compare and identify a generic subject to a database was rather limited since the typical error in object recognition was around 28% as compared to typical human error rate of about 5%. However, multiple neuromorphic algorithms progressively decreased this error to the 2.3% level by 2017, well below the human error rate! This has led to a worldwide flourishing biometrics market. Artificial intelligence and machine learning (AI/ML) will continue to revolutionize how computers operate and the market for facial biometrics is expected to reach the vicinity of \$700M in 2022.

Artificial intelligence and machine learning (AI/ML) will continue to revolutionize how computers operate. Face recognition by machines has been demonstrated to be better than humans by achieving an error rate of 2% or less vs. a

typical human error rate of 5%. Under these conditions the market for Facial Biometrics is expected to reach the vicinity of \$700M in 2022. See Figure ES21.

Figure ES21 Facial Biometrics is becoming an intrinsic part of society security

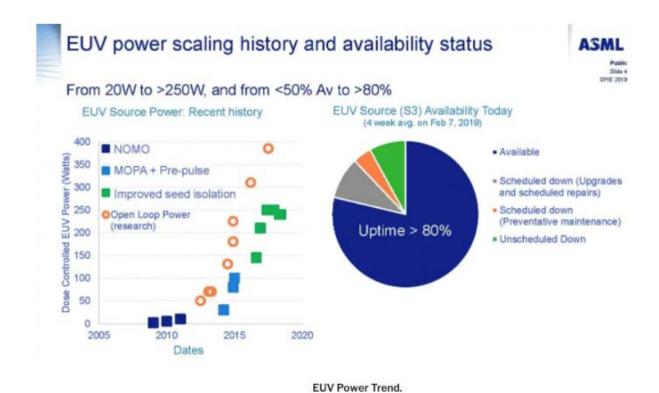

Clever circuit architecture, feature-down scaling and high yielding larger die were and remain at the foundation of Moore's Law since the mid-60s. In order to image progressively smaller features on a wafer it had been necessary in time to introduce lithography exposure tools with lenses of progressively higher numerical apertures (NAs) and illumination sources with smaller wavelengths. However, the relentless pace of introducing new technologies every two years strained the equipment community and the suppliers ran out of technology for new tools capable of using exposure wavelengths smaller than 193 nm. As far back as 1997 research activities on development of exposure tools operating at 13.5 nm illumination (classified under the category of extreme ultraviolet (EUV) were initiated by the EUV LLC under the leadership of Intel. The first fully working prototype was successfully demonstrated in April 2001. However, development of EUV tools progressed at a very slow pace. The main limiting factor consisted in weakness of power sources capable only of operating in the few watts range as opposed to the hundreds of watts required to expose wafers fast enough to reach economically viable levels. Semiconductor manufacturers faced with these problems were compelled to expose several layers in the complex manufacturing process more than one time by using interlaced patterns to produce the required lines and spaces.

A viable EUV source capable of delivering 200 watts was finally introduced and 11 EUV units were shipped in 2017 and adopted into several pilot lines in 2018. In 2022, 42 EUV tools were delivered to high-volume manufacturing lines. According to ASML, in 2021, these tools were able to resolve lines and spaces with a 30 nm pitch on a single exposure. In total 128 EUV units have been shipped by ASML as of the end of 2021. This means that this year (2022) the semiconductor industry will transition in the 12 nm technology generation according to the correct definition of technology node. The industry misnamed this technology generation as the "3 nm" generation (See Section 1.2.2 for a more detailed explanation). See Figure ES22.

Figure ES22 EUV source power exceeding 200W and uptime of over 80% opened the way for EUV introduction into manufacturing

Before the advent of EUV single exposure the semiconductor manufacturers were compelled to a work around consisting in multiple exposure for many critical layers to obtain the desired pitch

|               | Intel's 10nm  | Metal Stack |            |    |   |    |

|---------------|---------------|-------------|------------|----|---|----|

| Layer         | Metal         | Pitch       | Patterning | L  | М | Т  |

| Fin           |               | 34 nm       | Quad       | 1  | 4 | 4  |

| Gate          | Copper/Cobalt | 43-54 nm    | Dual       | 1  | 2 | 2  |

| Metal 0       | Cobalt        | 40          | Quad       | 1  | 4 | 4  |

| Metal 1       | Cobalt        | 36          | Quad       | 1  | 4 | 4  |

| Metal 2, 3, 4 | Copper        | 44          | Dual       | 3  | 2 | 6  |

| Metal 5       | Copper        | 52          | Dual       | 1  | 1 | 2  |

| Metal 6       | Copper        | 84          | Single     | 1  | 1 | 1  |

| Metal 7, 8    | Copper        | 112         | Single     | 2  | 1 | 2  |

| Metal 9, 10   | Copper        | 160         | Single     | 2  | 1 | 2  |

| Thick Metal 0 | Copper        | 1080        | Single     | 1  | 1 | 1  |

| Thick Metal 1 | Copper        | 11000       | Single     | 1  | 1 | 1  |

|               |               |             |            | 15 |   | 29 |

Figure ES23 Mask number using multiple 193 nm lithography doubled in the past five years

This workaround was quite viable to manufacture wafers, but it implied continually increasing manufacturing costs, as more and more layers required multiple exposures practically doubling the number of masks in some cases (Figure ES23); also, this solution implied acquiring more tools and manufacturing costs soon became inconsistent with cost targets of NAND memory producers. Under these conditions, memory manufacturers had to develop a different type of workaround to avoid increasing the number of masks by stacking multiple memory cells on top of each other to reach density goals while avoiding using the most advanced and expensive lithography. Stacks of almost 200 memory cells have been successfully demonstrated but logic producers have not yet embraced this device stacking solution into manufacturing even though multiple research papers were presented in last two-three years on this subject. (See Figure ES24.)

Source: Samsung

Figure ES24 3D NAND evolution: from 32 layers in 2015 to over 1000 layers by 2030

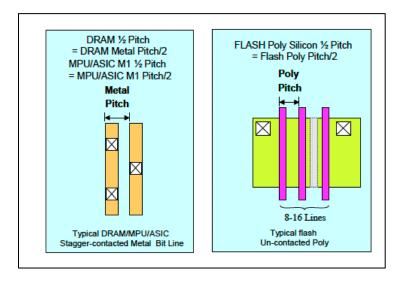

#### 1.2.2. Bringing the node nomenclature back to normal

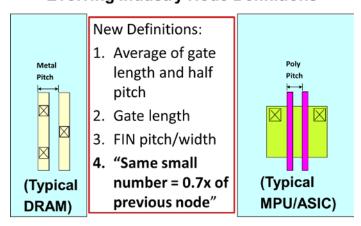

From 1992 to present the methodology to name technology nodes followed the NTRS, ITRS, and IRDS definition. The name of technology nodes is associated with the one half of the dimension of the smallest pitch typically utilized by the densest metal layer to be found in any integrated circuit. Figure ES25 illustrates the very first original definition of node: half pitch of the tightest metal layer. In the 1970s, 80s and the most of the 90s the dimensions of the gate length and of the half-pitch of the tightest metal lines were essentially the same therefore, this value was chosen as the node name since it conveyed with a single number the concept of density (i.e., half pitch of metal layer that correlated with transistor density) and the concept of performance (i.e., shorter polysilicon gate correlated with faster transistors). Typically, with the introduction of a new technology generation these dimensions were reduced to a value equal to 70% of the corresponding dimensions of the previous generation.

Figure ES25 Original technology node definition

In the second half of the 90s the adoption of the PC by the consumers imposed higher expectations of higher transistor density and higher performance with any new product introduction. As a result, in the 90s the introduction of microprocessor technologies accelerated from the previous 3–4-year cycle to a 2-year cycle to respond consumers' demands. As software programs became larger and more complex and therefore requiring higher execution speed it became necessary to reduce the channel length of the transistors more systematically and aggressively to 60% of the previous generation in order to produce faster transistors operating at higher frequencies. During this highly competitive time few companies began averaging the metal half-pitch dimension with the gate length dimension to define the name of the node associated with their newest technologies that appeared (on paper) smaller because of this averaging process (i.e., 70% half metal pitch reduction and 60% gate reduction led to a virtual 65% smaller node name) to attract the attention of the customers on more aggressive specifications than historical. Later, some companies decided to use only the gate dimension to define the name of the technology node. Finally, the technology node definition became 70% of whatever the name of the node of the previous generation was! (See Figure ES26.)

# **Evolving Industry Node Definitions**

Figure ES26 Industry "adaptation" of technology node definition

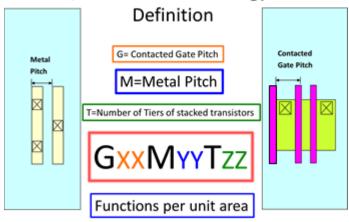

This nomenclature has led to a complete detachment between IC features and technology nodes' names. In fact, there are companies nowadays announcing the introduction in the non-too-distant future of technologies below 1 nm in this decade!? It is therefore beneficial to go back to basics and revitalize the node definition to represent reality more closely. The IRDS has adopted a broader definition of node but still related to the NTRS and ITRS historical definition. This is illustrated in Figure ES27.

# NTRS/ITRS->IRDS Technology Node

Figure ES27 IRDS comprehensive technology node definition

| YEAR OF PRODUCTION                                    | 2022     | 2025     | 2028              | 2031                    | 2034                    | 2037                    |

|-------------------------------------------------------|----------|----------|-------------------|-------------------------|-------------------------|-------------------------|

|                                                       | G48M24   | G45M20   | G42M16            | G40M16 T2               | G38M16 T4               | G38M16 T6               |

| Logic industry "Node Range" Labeling                  | "3nm"    | "2nm"    | "1.5nm"           | "4.0nm eq"              | "0.7nm eq"              | "0.5nm eq"              |

| Fine-pitch 3D integration scheme                      | Stacking | Stacking | Stacking          | 3DVLSI                  | 3DVLSI                  | 3DVLSI                  |

| Logic device structure options                        | finFET   | LGAA     | LGAA              | LGAA-3D                 | LGAA-3D                 | LGAA-3D                 |

| Logic device structure options                        | LGAA     | LGAA     | CFET-SRAM         | CFET-SRAM               | CFET-SRAM               | CFET-SRAM               |

| Platform device for logic                             | finFET   | LGAA     | LGAA<br>CFET-SRAM | LGAA-3D<br>CFET-SRAM-3D | LGAA-3D<br>CFET-SRAM-3D | LGAA-3D<br>CFET-SRAM-3D |

|                                                       | Cure     | Ouse     | Oute              | tier tier tier tier     | ther ther ther there    | One One                 |

| LOGIC DEVICE GROUND RULES                             |          |          |                   |                         |                         |                         |

| Mx pitch (nm)                                         | 32       | 24       | 20                | 16                      | 16                      | 16                      |

| M1 pitch (nm)                                         | 32       | 23       | 21                | 20                      | 19                      | 19                      |

| MO pitch (nm)                                         | 24       | 20       | 16                | 16                      | 16                      | 16                      |

| Gate pitch (nm)                                       | 48       | 45       | 42                | 40                      | 38                      | 38                      |

| Lg: Gate Length - HP (nm)                             | 16       | 14       | 12                | 12                      | 12                      | 12                      |

| Lg: Gate Length - HD (nm)                             | 18       | 14       | 12                | 12                      | 12                      | 12                      |

| Channel overlap ratio - two-sided                     | 0.20     | 0.20     | 0.20              | 0.20                    | 0.20                    | 0.20                    |

| Spacer width (nm)                                     | 6        | 6        | - 5               | 5                       | 4                       | 4                       |

| Spacer k value                                        | 3.5      | 3.3      | 3.0               | 3.0                     | 2.7                     | 2.7                     |

| Contact CD (nm) - finFET, LGAA                        | 20       | 19       | 20                | 18                      | 18                      | 18                      |

| Device architecture key ground rules                  |          |          |                   |                         |                         |                         |

| Device lateral pitch (nm)                             | 24       | 26       | 24                | 24                      | 23                      | 23                      |

| Device height (nm)                                    | 48       | 52       | 48                | 64                      | 60                      | 56                      |

| FinFET Fin width (nm)                                 | 5.0      | JE       | 40                | - 04                    | - 00                    | - 50                    |

| Footprint drive efficiency - finFET                   | 4.21     |          |                   |                         |                         |                         |

| Lateral GAA vertical pitch (nm)                       | 4.21     | 18.0     | 16.0              | 16.0                    | 15.0                    | 14.0                    |

| Lateral GAA (nanosheet) thickness (nm)                |          | 6.0      | 6.0               | 6.0                     | 5.0                     | 4.0                     |

| Number of vertically stacked nanosheets on one device |          | 3        | 3                 | 4                       | 5.0<br>4                | 4.0                     |

|                                                       |          | 30       |                   |                         |                         |                         |

| LGAA width (nm) - HP                                  |          |          | 30                | 20                      | 15                      | 15                      |

| LGAA width (nm) - HD                                  |          | 15       | 10                | 10                      | 6                       | 6                       |

| LGAA width (nm) - SRAM                                |          | 7        | 6                 | 6                       | 6                       | 6                       |

| Footprint drive efficiency - lateral GAA - HP         |          | 4.41     | 4.50              | 5.47                    | 5.00                    | 4.75                    |

| Device effective width (nm) - HP                      | 101.0    | 216.0    | 216.0             | 208.0                   | 160.0                   | 152.0                   |

| Device effective width (nm) - HD                      | 101.0    | 126.0    | 96.0              | 128.0                   | 88.0                    | 80.0                    |

| PN seperation width (nm)                              | 45       | 40       | 20                | 15                      | 15                      | 10                      |

Notes: Mx—Tight-pitch routing metal interconnect IDM—independent device manufacturer FinFET—fin field-effect transistor LGAA—lateral gate all around EUV—extreme ultraviolet NA—numerical aperture Ge—germanium SiGe—silicon germanium RMG—replacement metal gate VLSI—very large-scale integration W2W—wafer to wafer D2W—die to wafer Mem-on-Logic—memory on logic

Figure ES28 Devices will continue to aggressively scale in the next 5 years

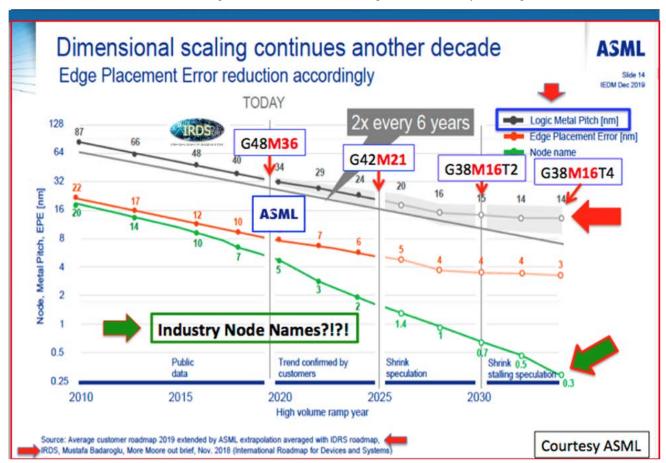

The top line of Figure ES28 refers to the year in which the technology is introduced into manufacturing. The second line indicates the key node attributes. G indicates the dimension of the contacted gated pitch while M indicates the dimension of the tightest metal pitch. *The third line indicates the "industry labeling" of nodes that clearly appears to be completely disconnected from reality*. This is best illustrated by the recent presentation made by ASML in cooperation with IRDS reported below (Figure ES29)

It should be noted once again that reduction of gate length dimension by itself is no longer a dominant influence on the performance of logic circuits. This is due to the severe power limitations that emerged in the middle of the previous decade. In order to limit power values to the 120-130 W range (i.e., no wafer cooling needed) it was no longer possible to increase operational frequency beyond 10 GHz and therefore faster transistors no longer translated into to a higher operating frequency as shown earlier in Figure ES20. For this reason, semiconductor companies concentrated the transistor design effort on reducing power consumption instead of maximizing transistor speed since IC power dissipation had become such a major design constraint. However, reduction in contacted gate pitch is essential to increasing transistor density.

In few words, transistors are still getting faster generation-to-generation but not at the same rate than what used to be achieved in the 90s, since the major emphasis in transistor design has now shifted from speed to limiting power consumption.

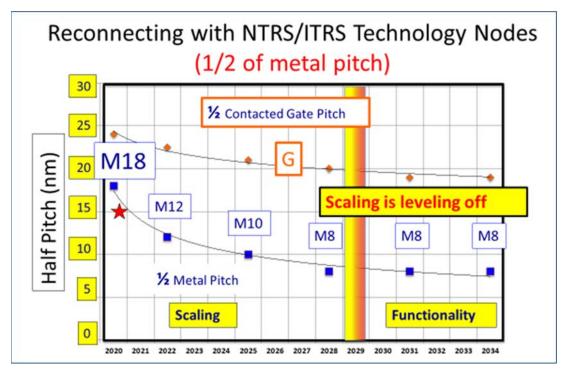

It is however possible to fully reconnect with the historical definition of technology node defined by NTRS/ITRS if the value of the metal half pitch is once again used to identify a technology generation (Figures ES27 and ES28). It is clear from this picture that the semiconductor industry is not in the 7 nm or 10 nm generation but barely in the 18 nm generation!

No wonder Moore's Law will be still valid for the next 10 years, once the real numbers of IC features are used for node definition; there is still a lot of room to run for scaling as a contributor to increasing transistor density!(See Figures ES29 and ES30)

Figure ES29 Consistent definition and trend of metal half-pitch reported by ASML and IRDS

Figure ES30

Metal pitch scaling exceeding expectation in 2020!

Figure ES30 shows also that feature scaling will reach fundamental limits of around 7-8 nm at the end of this decade. This prediction is consistent with forecasts of equipment technology leaders.<sup>2</sup> However, by early 2030 it is expected that quantum-computing technologies will begin to make real contributions to the advancement of the electronics industry. (See Section 1.4.)

## 1.2.3. 5G AND BEYOND ROADMAP HAS BECOME THE "INTERNATIONAL NETWORK GENERATIONS ROADMAP"!

Cell phones began operation in the 90s using frequencies in the 800-900 MHz ranges in accordance with specifications of the Global System for Mobile Communications (GSM). These operational frequencies utilized by cell phones have increased multiple times and have now reached the present revision named 4G and LTE that operate in the 2,500-2,700 MHz ranges.

The adoption of a more powerful communication infrastructure under the name of 5G has been under discussion for the past few years. In 5G the utilization of frequencies ranging from 3 to 28 GHz and beyond had been under discussion for some time. In 2017 it became clear that 5G expectations and therefore its definition was quickly becoming by far much more complex that any of the previous transitions and therefore IEEE decided to launch a new network roadmap aimed at 5G.

In 2018 the working groups engaged in this IEEE network roadmap effort realized that the transition to 5G was no longer limited to the deployment of a communication system that introduced a new frequency spanning from 3.7 GHZ to 4.2 GHz for cell phones but it was much more than that.

5G defined a very broad new platform covering multiple aspects of communications. For instance, multiple bands operating in the 20–40 GHz and ~60 GHZ ranges were also proposed as additional elements of 5G. Therefore, the IEEE network roadmapping effort was renamed the **International Network Generations Roadmap** (**INGR**) in 2020 to encompass a much broader range of frequencies and novel network solutions. Close cooperation between IRDS and INGR has continued throughout the past two years.

As stated before, operation in these frequency ranges is still well within the capabilities of ICs. In the past 10 years, cell phones, portable PCs and many types of mobile appliances have become a viable means of accessing the Internet. Cell phone power consumption is typically below 5 watts, so this value is well within the thermal limits of IC operations. In the past 10 years access to the Internet via 4G-LTE or Wi-Fi5 has been continuously increasing since the areas of wireless coverage are continuously

THE INTERNATIONAL ROADMAP FOR DEVICES AND SYSTEMS: 2022 COPYRIGHT © 2022 IEEE. ALL RIGHTS RESERVED.

<sup>&</sup>lt;sup>2</sup> Martin van den Brink/President and CTO. ASML Keynote. "Continued scaling in semiconductor manufacturing enabled by advances in lithography". San Francisco, IEDM 2019.

extending due to proliferation of hundreds of thousands cell towers and therefore mobile appliances have become the most convenient means of communication and access to any source of information anywhere at any time. Deployment of 5G (operating around 4 GHz) is in full progress limited only by the rate at which new cell towers can be installed since the typical radius of communication is drastically reduced. Additionally, Wi-Fi6 (operating around 6 GHz) has also been deployed.

However, even though Wi-Fi5/6 and 4G-LTE and 5G were developed with completely different market models and applications (i.e., wireless access to the Internet and cell phone, respectively) it is quite clear that both technologies are now interchangeably used, and they are both contending for access to the same range of frequencies. This contention is particularly fierce in the "last mile" to conquer the market for access to the homes and public buildings In addition, distribution of TV programs, which early on relied exclusively on "wireless communications," is also contending for new network solutions. So, cell phone companies, cable distributors and content providers are all contending for consumer attention. Is this a recipe for some type of unification and/or consolidation among all these business models? The question remains on how it will be possible to reconcile different business models that support different applications.

### 1.2.4. DATA CENTERS

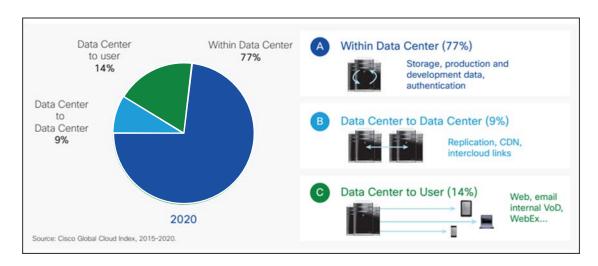

The insatiable demand for information has led to the creation of gigantic clusters of servers and memory banks named "data centers" (Figure ES31). In this environment performance is still fundamental and using complex cooling systems can mitigate power issues. Power consumption of data centers is rapidly escalating into the hundreds of megawatts range. Communications within the data centers and for long distances is handled via fiber optics because of their stellar low rate of attenuation but traffic within data centers remains a bottleneck (Figure ES32).

Figure ES31 Data center growth continues to accelerate

Figure ES32 Traffic within data center is main limiting factor

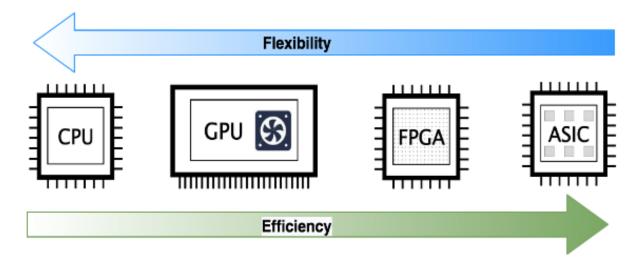

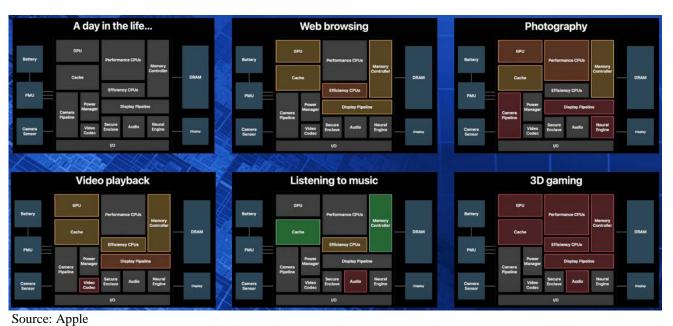

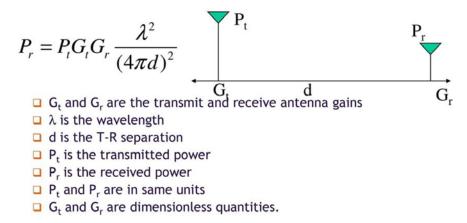

Adoption of multicore processors has also found the perfect application in servers used in data centers. In the past a separate bank of processors and memory aimed at a specific application had to be separately installed on a specific rack because the operating system required by the application was different from the operating system used for other applications. Under these conditions utilization of processors and memory devices was very inefficient. The advent of multicore processors, however, offered the opportunity to "host" different operating systems in each of the cores residing within the same microprocessor and therefore led to a dramatic increase in efficiency.