### UNIVERSITY OF CALIFORNIA

### Santa Barbara

Ant Colony Metaheuristics for Fundamental Architectural Design Problems

A Dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Electrical and Computer Engineering

by

Gang Wang

Committee in charge:

Professor Ryan Kastner, Chair

Professor Malgorzata Marek-Sadowska

Professor Steve Butner

Professor Elaheh Bozorgzadeh

Professor Timothy Sherwood

September 2007

### The dissertation of Gang Wang is approved:

| Chair | Date |

|-------|------|

|       |      |

|       |      |

|       | Date |

|       |      |

|       |      |

|       | Date |

|       |      |

|       |      |

|       | Date |

|       |      |

|       |      |

|       |      |

|       | Date |

University of California, Santa Barbara

September 2007

Ant Colony Metaheuristics for Fundamental Architectural Design Problems

Copyright 2007

by

Gang Wang

To my wife Fang Liu,

my children James, Justin, Jocelyn,

and my parents Tihao Wang and Shuchun Li.

### **Abstract**

Ant Colony Metaheuristics for Fundamental Architectural Design Problems

by

### Gang Wang

Doctor of Philosophy in Electrical and Computer Engineering

University of California, Santa Barbara

Professor Ryan Kastner, Chair

As the fabrication technology advances, the number of transistors in modern computer systems keeps growing exponentially. This growth creates tremendous potential while imposing big challenges to the electronic design automation community on how to construct such complicated systems. In order to effectively utilize the computing resources, a number of fundamental problems need to be addressed. As the scale and complexity of these problems grow, we must look towards new optimizations methods, rather than simply perform iterative improvements on existing techniques.

In this dissertation, I will report our research work on constructing new heuristic algorithms using the Ant Colony metaheuristic for effectively and efficiently solving a range of difficult architectural design problems. We investigate three  $\mathcal{NP}$ -hard problems in this context, namely system partitioning, operation scheduling and design space exploration. Results show that Ant Colony metaheuristic is a very promising approach for solving these problems, and the algorithms we propose generally achieve better quality solutions with much improved stability compared to conventional methods.

Moreover, by establishing the theoretical link between timing and resource constrained scheduling, we propose an effective design exploration framework that leverages duality between the scheduling problems. To our best knowledge, our work is the first extensive study on applying the Ant Colony metaheuristics to the architectural design field.

## Acknowledgments

I would like to show my sincerest gratitude to my advisor Professor Ryan Kastner for giving me copious amounts of insightful guidance, constant encouragement, constructive criticism, and expertise on every subject that arose throughout all these years. His enthusiasm and dedication to his students are truly inspiring; it is my very privilege to have been one of them. I would also like to thank Professor Malgorzata Marek-Sadowska, Professor Elaheh Bozorgzadeh, Professor Steven Butner, and Professor Tim Sherwood for being on my Ph.D. committee and for all their helps along the way.

I am very thankful for the many friends and fellow students I have had at UCSB, including Anup Hosangadi, Yen Meng, Brian DeRenzi, for their many stimulating discussions and warm friendship. Particularly, I want to thank Wenrui Gong, who I collaborated with on numerous research efforts and became close friend with over the years. Without them, my experience at UCSB won't be as rewarding as it is.

Finally, I want to thank my wife, Fang Liu, for her love, support, encouragement, sense of humor, and for being an intelligent partner on my research journey as well. I could not have accomplished this without her. Very special thanks to my parents for their selfless love and support, and to my lovely children James, Justin and Jocelyn.

### **Curriculum Vitæ**

Gang Wang was born in Shaanxi, China in 1971. He received the Bachelor of Electrical Engineering degree from Xian Jiaotong University in 1992, and Master of Computer Science degree from Chinese Academy of Sciences in 1995, both in China. From 1995 to 1997, he conducted research work at Michigan State University (East Lansing, MI, US), and Carnegie Mellon University (Pittsburgh, PA, US), focusing on speech and image understanding. Since 1997, Mr. Wang held positions as software architect and technical manager in different leading companies of medical industry, including Computer Motion, Intuitive Surgical and Karl Storz Endoscope. His work focused on the research and development of complex surgical robotics systems, multi-modal human-computer interaction and intelligent operating room. His current research interests include reconfigurable and embedded computing, optimization algorithms and their applications, novel architectural design for FPGA and nanocomputing platforms, ubiquitous computing and its applications in medical/healthcare systems. He has authored or co-authored more than 20 technical papers in different journals and conferences on related topics.

#### **Related Publications:**

BOOKS/BOOK CHAPTERS

[B1] Gang Wang, Wenrui Gong, and Ryan Kastner. Operation Scheduling: Algorithms and Design Space Exploration, to appear in High Level Synthesis Handbook: The State of Arts published by Springer.

JOURNAL ARTICLES

- [J1] Gang Wang, Wenrui Gong, Brian DeRenzi, and Ryan Kastner. Exploring

Time/Resource Tradeoffs by Solving Dual Scheduling Problems with the Ant

Colony Optimization, accepted by ACM Transactions on Design Automation

of Electronic Systems (TODAES).

- [J2] Gang Wang, Wenrui Gong, Brian DeRenzi, and Ryan Kastner. Ant Scheduling Algorithms for Resource and Timing Constrained Operation Scheduling, IEEE Transactions of Computer-Aided Design of Integrated Circuits and Systems (TCAD), Vol 26, Issue 6, pp 1010-1029, 2006.

- [J3] **Gang Wang**, Satish Sivaswamy, Cristinel Ababei, Kia Bazargan, Ryan Kastner and Eli Bozorgzadeh. *Statistical Analysis and Design of HARP Routing Pattern FPGAs*, *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems* (TCAD), Vol 25, Issue 10, pp 2088-2102, October 2006.

- [J4] **Gang Wang**, Wenrui Gong and Ryan Kastner, *Application Partitioning on Programmable Platforms Using the Ant Colony Optimization*, *Journal of Embedded Computing* (JEC), Vol 2, Issue 1, pp 119-136, 2006.

#### PEER-REVIEWED CONFERENCE/WORKSHOP PAPERS

- [C1] Ted Huffmire, Brett Brotherton, Gang Wang, Ryan Kastner, and Tim Sherwood. Moats and Drawbridges: An Isolation Primitive for Reconfigurable Hardware Based Systems, IEEE Symposium on Security and Privacy, 2007.

- [C2] Gang Wang, Wenrui Gong, and Ryan Kastner, On the Use of Bloom Filters for Defect Maps in Nanocomputing, In International Conference on

- Computer-Aided Design (ICCAD), 2006.

- [C3] Gang Wang, Wenrui Gong, Brian DeRenzi and Ryan Kastner, Design Space Exploration using Time and Resource Duality with the Ant Colony Optimization, In 43rd Design Automation Conference (DAC), 2006.

- [C4] Gang Wang, Wenrui Gong, and Ryan Kastner, Defect-Tolerant Nanocomputing Using Bloom Filters for Defect Mapping, In IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM), pp 277-278, 2006.

- [C5] Wenrui Gong, **Gang Wang** and Ryan Kastner. Storage Assignment During High-level Synthesis for Configurable Achitectures, In International Conference on Computer Aided Design (ICCAD), 2005.

- [C6] Gang Wang, Wenrui Gong and Ryan Kastner, Instruction Scheduling using MAX-MIN Ant Optimization, In ACM Great Lakes Symposium on VLSI (GLSVLSI), 2005.

- [C7] Satish Sivaswamy, **Gang Wang**, Cristinel Ababei, Kia Bazargan, Ryan Kastner, Eli Bozorgzadeh. *HARP: hard-wired routing pattern FPGAs*, In *Proceedings of the ACM/SIGDA 13th International Symposium on Field Programmable Gate Arrays* (FPGA), 2005.

- [C8] Wenrui Gong, Yan Meng, **Gang Wang**, Ryan Kastner, and Timothy Sherwood, *Data Partitioning for Reconfigurable Architectures with Distributed Block RAM*, In *International Conference on Engineering of Reconfigurable*

- Systems and Algorithms (ERSA), 2005.

- [C9] Wenrui Gong, Gang Wang, and Ryan Kastner. Data Partitioning for Reconfigurable Architectures with Distributed Block Ram, In The Fourteenth International Workshop on Logic and Synthesis (IWLS), 2005.

- [C10] Gang Wang, Wenrui Gong and Ryan Kastner. System Level Partitioning for Programmable Platforms Using the Ant Colony Optimization, In 13th International Workshop on Logic and Synthesis (IWLS), 2004.

- [C11] Wenrui Gong, **Gang Wang** and Ryan Kastner. A High Performance Application Representation for Reconfigurable Systems, In the International Conference on Engineering of Reconfigurable Systems and Algorithms (ERSA), 2004.

- [C12] Gang Wang, Wenrui Gong and Ryan Kastner, A New Approach for

Task Level Computational Resource Bi-Partitioning, In 15th IASTED

International Conference on Parallel and Distributed Computing and

System (PDCS), 2003. (Best paper nomination.)

# **Contents**

| Li | ist of l | Figures       |                                         |  |  |   | XV   |

|----|----------|---------------|-----------------------------------------|--|--|---|------|

| Li | ist of ' | <b>Fables</b> |                                         |  |  | 2 | xvii |

| Li | ist of A | Algorith      | ıms                                     |  |  | X | viii |

| 1  | Intr     | oductio       |                                         |  |  |   | 1    |

|    | 1.1      | Motiva        | ation                                   |  |  |   | 1    |

|    | 1.2      | Resear        | ch Overview                             |  |  |   | 6    |

|    | 1.3      | Organi        | ization of Dissertation                 |  |  |   | 10   |

| 2  | Ant      | Colony        | Metaheuristic                           |  |  |   | 12   |

|    | 2.1      | Nature        | Inspired Metaheuristics                 |  |  |   | 12   |

|    | 2.2      |               | For Travel Salesman Problem             |  |  |   | 17   |

|    | 2.3      | ACO f         | For Other Combinatory Problems          |  |  |   | 19   |

|    | 2.4      | Conve         | rgency of ACO Method                    |  |  |   | 21   |

|    | 2.5      | MAX-          | MIN Ant System (MMAS)                   |  |  |   | 23   |

| 3  | Syst     | em Par        | titioning                               |  |  |   | 26   |

|    | 3.1      | Introdu       | uction                                  |  |  |   | 27   |

|    | 3.2      | ACO f         | For System Partitioning                 |  |  |   | 31   |

|    |          | 3.2.1         | Problem Definition                      |  |  |   | 31   |

|    |          | 3.2.2         | Augmented Task Graph                    |  |  |   | 34   |

|    |          | 3.2.3         | ACO Formulation for System Partitioning |  |  |   | 36   |

|    |          | 3.2.4         | Complexity Analysis                     |  |  |   | 42   |

|    |          | 3.2.5         | Extending the ACO/ATG method            |  |  |   | 42   |

|    |          | 3.2.6         | Comparing with the Original ACO         |  |  |   | 44   |

|    | 3.3      | Experi        | mental Results and Performance Analysis |  |  |   | 46   |

|    |          | 3.3.1         | Target Architecture and Benchmarks      |  |  |   | 46   |

|    |          | 3.3.2         | Absolute Quality Assessment             |  |  |   | 50   |

|    |          | 3.3.3         | Comparing with Simulated Annealing      |  |  |   | 57   |

|   |      | 3.3.4 Hybrid ACO with Simulated Annealing                   | 60  |

|---|------|-------------------------------------------------------------|-----|

|   | 3.4  | Application: Quick Design Parameter Estimation              | 62  |

|   | 3.5  | Summary                                                     | 66  |

| 4 | Ope  | eration Scheduling                                          | 67  |

|   | 4.1  | Introduction                                                | 68  |

|   | 4.2  | Preliminaries                                               | 72  |

|   |      | 4.2.1 Operation Scheduling Problem Definition               | 72  |

|   |      | 4.2.2 Related Work                                          | 74  |

|   | 4.3  | ACO for Timing Constrained Scheduling                       | 77  |

|   |      | 4.3.1 Force-Directed Scheduling                             | 77  |

|   |      | 4.3.2 Algorithm Formulation                                 | 80  |

|   |      | 4.3.3 Refinements                                           | 86  |

|   |      | 4.3.4 Extensions                                            |     |

|   |      | 4.3.5 Complexity Analysis                                   |     |

|   | 4.4  | ACO for Resource Constrained Scheduling                     |     |

|   |      | 4.4.1 List Scheduling                                       |     |

|   |      | 4.4.2 Algorithm Formulation                                 |     |

|   |      | 4.4.3 Refinements                                           |     |

|   |      | 4.4.4 Extensions                                            |     |

|   |      | 4.4.5 Complexity Analysis                                   |     |

|   | 4.5  | ExpressDFG Benchmarks                                       |     |

|   | 4.6  | Experimental Results                                        |     |

|   |      | 4.6.1 Time Constrained Scheduling                           |     |

|   |      | 4.6.2 Resource Constrained Scheduling                       |     |

|   |      | 4.6.3 Comparison with Simulated Annealing                   |     |

|   |      | 4.6.4 Parameter Sensitivity                                 |     |

|   | 4.7  | Summary                                                     | 133 |

| 5 | Desi | ign Space Exploration                                       | 136 |

|   | 5.1  |                                                             |     |

|   | 5.2  | Related Work                                                |     |

|   | 5.3  | Exploration Using Time and Resource Constrained Duality     |     |

|   |      | 5.3.1 Iterative Design Space Exploration Leveraging Duality | 142 |

|   |      | 5.3.2 Integrate with ACO-based Scheduling Algorithms        | 147 |

|   | 5.4  | Experiments and Analysis                                    |     |

|   |      | 5.4.1 Benchmarks and Setup                                  | 149 |

|   |      | 5.4.2 Quality Assessment                                    | 150 |

|   | 5.5  | Summary                                                     | 159 |

| 6 | Con  | clusions and Future Work                                    | 160 |

|   | 6.1  | Conclusions                                                 | 160 |

|   | 6.2  | Future Work                                                 | 163 |

Bibliography 165

# **List of Figures**

| A simplified representation of an FPGA fabric is on the left. Configurable Logic Blocks (CLBs) perform logic level computation using Lookup Tables (LUTs) for bit manipulations and flipflops for storage. The switch boxes and routing channels provide connections between the CLBs. SRAM configuration bits are used throughout the FPGA (e.g., to program the logical function of the LUTs and connect a segment in one routing channel to a segment in an adjacent routing channel). The FPGA floor plan on the right illustratively shows a physical layout of FPGA after routing | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) A laboratory nest of a Leptothorax ant colony; (b) Experiment set-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6 2 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| (1) Single ant constructs a solution; (2) Multiple solutions are constructed by all the ants individually; (3) The pheromone trails adaptively adjust their values during the iterations; (4) The optimal solution emerges as the search learns from its experience                                                                                                                                                                                                                                                                                                                     | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

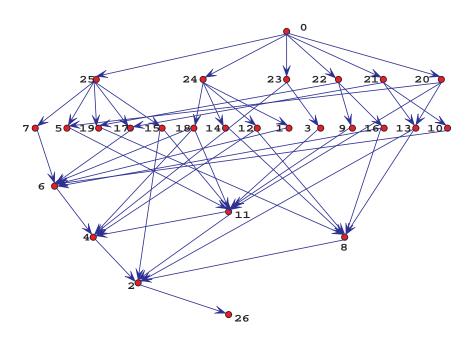

| ATG for 3-way Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

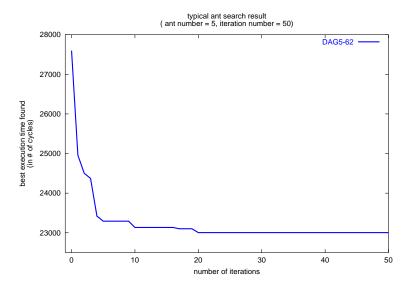

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

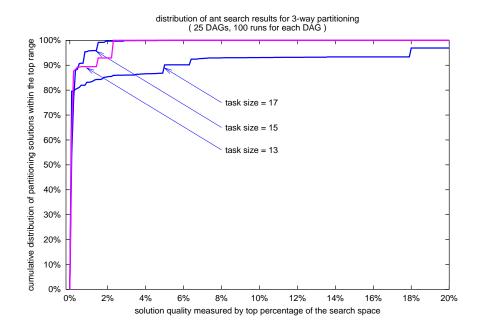

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Estimate Design Parameters with ACO application partitioner on de-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| sign choice with incremented resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | figurable Logic Blocks (CLBs) perform logic level computation using Lookup Tables (LUTs) for bit manipulations and flipflops for storage. The switch boxes and routing channels provide connections between the CLBs. SRAM configuration bits are used throughout the FPGA (e.g., to program the logical function of the LUTs and connect a segment in one routing channel to a segment in an adjacent routing channel). The FPGA floor plan on the right illustratively shows a physical layout of FPGA after routing |

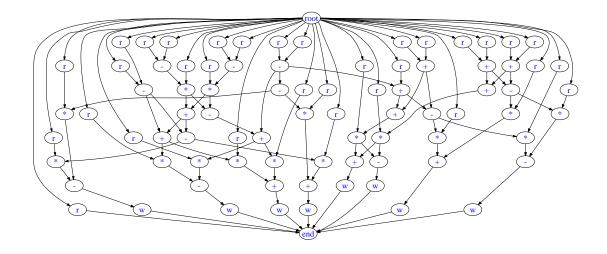

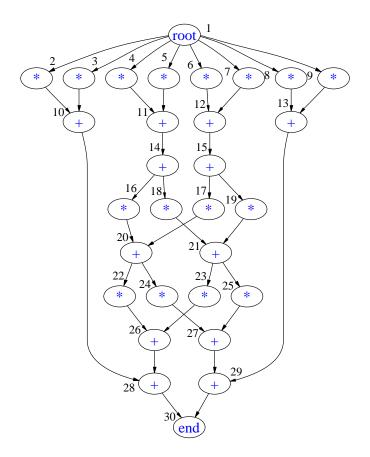

| 4.1 | Data Flow Graph (DFG) of the <i>cosine2</i> benchmark                                                                                                                                                                                                                                                                                                      |       |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|     | ('r' is for memory read and 'w' for memory write)                                                                                                                                                                                                                                                                                                          | . 74  |

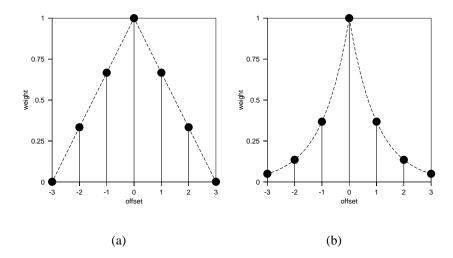

| 4.2 | Pheromone update windows                                                                                                                                                                                                                                                                                                                                   | . 87  |

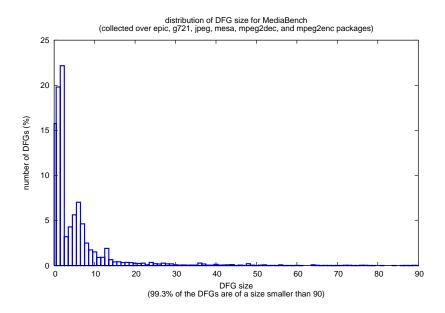

| 4.3 | Distribution of DFG size for MediaBench                                                                                                                                                                                                                                                                                                                    | . 105 |

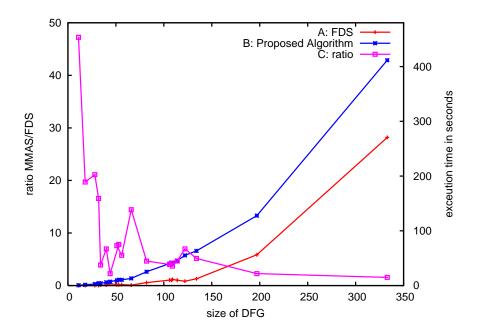

| 4.4 | Execution Time for Timing-Constrained Scheduling.                                                                                                                                                                                                                                                                                                          |       |

|     | (Ratio is MMAS time / FDS time)                                                                                                                                                                                                                                                                                                                            | . 114 |

| 4.5 | Data Flow Graph of AR Filter.                                                                                                                                                                                                                                                                                                                              |       |

|     | (The number by the node is the index assigned for the operation.)                                                                                                                                                                                                                                                                                          | . 123 |

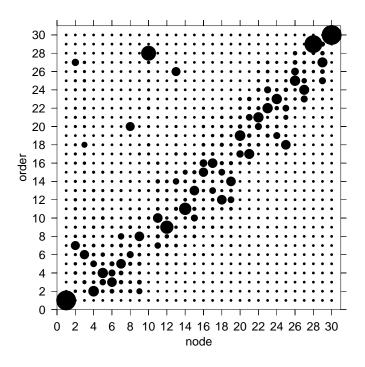

| 4.6 | Pheromone Heuristic Distribution for ARF                                                                                                                                                                                                                                                                                                                   | . 124 |

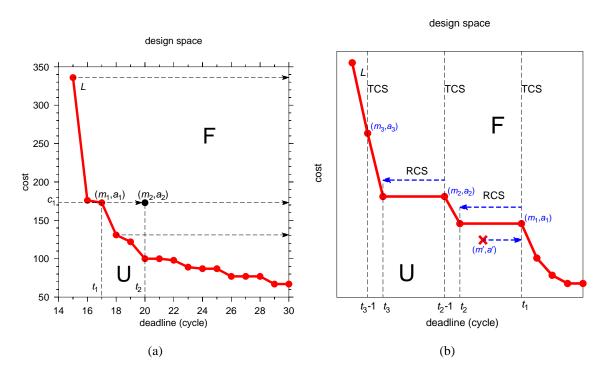

| 5.1 | Design Space Exploration Using Duality between Schedule Problems                                                                                                                                                                                                                                                                                           |       |

|     | (Curve $L$ gives the optimal time/cost tradeoffs.)                                                                                                                                                                                                                                                                                                         | . 142 |

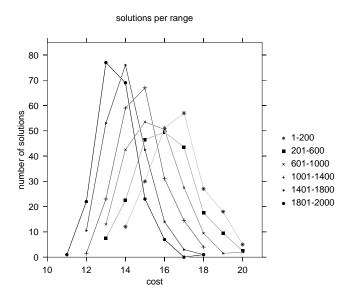

| 5.2 | Distribution of the TCS ACO solution quality on idetcol benchmark with a deadline set to its ASAP time. Each line shows a different phase of the algorithm execution where each point gives the number of solutions of a particular resource cost. The line "1-200" denotes the first 200 solutions found by the ACO algorithm, while the line "1801-2000" |       |

|     | gives last 200 solutions                                                                                                                                                                                                                                                                                                                                   | . 152 |

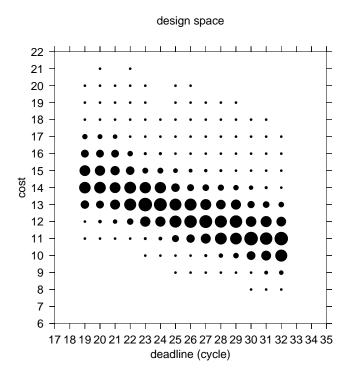

| 5.3 | Solution quality of the TCS ACO on the idetcol benchmark. We run                                                                                                                                                                                                                                                                                           |       |

|     | the TCS ACO algorithm at each deadline ranging from its ASAP time                                                                                                                                                                                                                                                                                          |       |

|     | (19) to (32). The size of the dot indicates the proportion of solutions                                                                                                                                                                                                                                                                                    |       |

|     | with a specific resource cost found at each deadline                                                                                                                                                                                                                                                                                                       | . 153 |

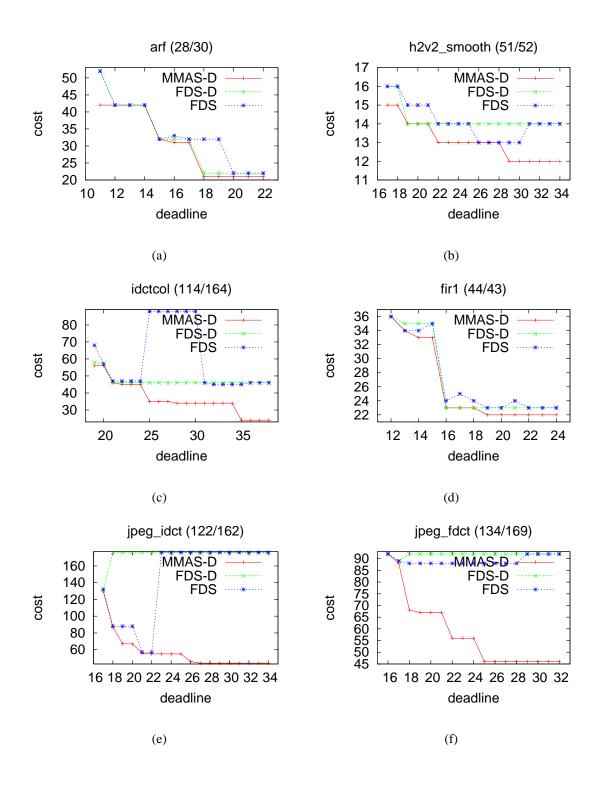

| 5.4 |                                                                                                                                                                                                                                                                                                                                                            |       |

|     | Design Space Exploration results: MMAS-D, FDS-D and FDS                                                                                                                                                                                                                                                                                                    | . 155 |

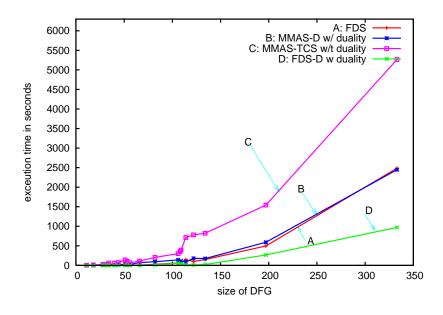

| 5.5 | Timing Performance Comparison                                                                                                                                                                                                                                                                                                                              | . 158 |

# **List of Tables**

| 2.1        | Applications of ACO method and their qualitative performance 21               |

|------------|-------------------------------------------------------------------------------|

| 3.1<br>3.2 | Comparing ACO results with the random sampling                                |

| 4.1        | ExpressDFG benchmark suite                                                    |

|            | (Benchmarks with † are extracted from MediaBench.)                            |

|            | (Benchmark node and edge count with the operation depth (OD) as-              |

|            | suming unit delay.)                                                           |

| 4.2        | Effect of Look-ahead Mechanism in FDS                                         |

|            | (Result shown in MUL/ALU number pair. Deadline is in cycles.) 109             |

| 4.3        | Partial detailed results for Timing-Constrained Scheduling                    |

|            | (Size is given as DFG's node/edge number pair. Virtual nodes and              |

|            | edges are not counted.                                                        |

|            | Average and standard deviation $\sigma$ are computed over 5 runs. Saving is   |

|            | computed based on FDS results. No weight applied.)                            |

| 4.4        | Result Summary for Timing-Constrained Scheduling                              |

|            | Data in parenthesis shows the results obtained using Simulated Anneal-        |

|            | ing.                                                                          |

|            | Deadline shows the tested range. Average $\sigma$ is computed over the tested |

|            | range.                                                                        |

|            | Saving is computed based on FDS results. No weight applied 112                |

| 4.5        | Result Summary for Homogenous Resource-Constrained Scheduling                 |

|            | (Heuristic Labels: OM=Operation Mobility OD=Operation Depth,                  |

|            | LWOD=Latency Weighted Operation Depth, SN=Successor Number) . 117             |

| 4.6 | Result Summary for Heterogenous Resource-Constrained Scheduling       |

|-----|-----------------------------------------------------------------------|

|     | Schedule latency is in cycles; Runtime is in seconds; † indicates     |

|     | CPLEX failed to provide final result before running out of memory.    |

|     | (Resource Labels: a=alu, fm=faster multiplier, m=mutiplier, i=input,  |

|     | o=output)                                                             |

|     | (Heuristic Labels: OM=Operation Mobility OD=Operation Depth,          |

|     | LWOD=Latency Weighted Operation Depth, SN=Successor Number) . 119     |

| 5.1 | Summary for Design Space Exploration Results. Each line gives         |

|     | the benchmark name, the tested time range and the results of each     |

|     | design space exploration algorithm (FDS-D, MMAS-TCS, MMAS-D           |

|     | compared to the exhaustive FDS result. (A negative result indicates a |

|     | smaller resource allocation, which is desired.)                       |

# **List of Algorithms**

| 1 | ACO Algorithm for System Partitioning                       | 37 |

|---|-------------------------------------------------------------|----|

| 2 | Force-Directed Scheduling for Time-Constrained Optimization | 81 |

| 3 | MMAS for Timing Constrained Scheduling                      | 85 |

| 4 | Resource-Constrained List Scheduling                        | 92 |

| 5 | MMAS for Resource-Constrained Scheduling                    | 96 |

| 6 | Simulated Annealing for Timing-Constrained Scheduling       | 28 |

| 7 | Iterative Design Space Exploration Algorithm                | 46 |

## **Chapter 1**

## Introduction

### 1.1 Motivation

Due to the rapid advances in VLSI fabrication technology, modern computer systems continue to provide better performance by effectively utilizing an increasing number of transistors on a chip. The well-known Moore's law [73], which predicts that the number of transistors on a single chip would grow exponentially over a relative short period of time, has been very accurate so far. Over the past 30 years, the transistor density has doubled every 18-24 months. ITRS estimates that we will be able to integrate more than half billion transistors on a 468 mm<sup>2</sup> chip by the year of 2009[85]. This creates tremendous potential for future computing systems.

This also imposes big challenges to the Electronic Design Automation (EDA) community on how to effectively build such complicated systems. As the complexity of

digital systems increases, so does the complexity of the underlying EDA problems. One critical question we need to address is: as computing resources become abundant, how can we effectively utilize these resources so that we can fully exploit the technology advances to solve future computing problem? For example, recent studies by Professor Cong's group at UCLA [20, 21], indicate that the results obtained over a benchmark circuits with known optimal wire lengths using the current commercially available routing and placement tools are far from the optimal. They argued that just by improving these results we are potentially able to move today's technology one generation ahead. While these examples are contrived, and follow-up study [64] shows that real-world designs are not as dire as initially suggested, this is still a staggering difference. As we move into smaller sub-micro technologies, there exists room for improvement for these algorithms.

In answering this challenge, one trend that seems to be affirmed in recent years is the shift to parallel architectural design or spatial computational model in constructing computing systems. This differs significantly from timeplexing a single active computation among a large number of operations as we have been familiar with in traditional single processor architectures. Spatial computational designs dedicate specific computing hardware to individual operations [24]. Operations are then interconnected in space rather than in time. This model will allow us to exploit the full parallelism available in the applications. The spatial computing model trades increased area for better time performance and effective overall usage of the computing resources.

The trend of shifting to spatial computing has also been evidenced by the steady market adoption of reconfigurable computing technologies, especially the Field Programmable Gate Array (FPGA) platform. Reconfigurable hardware, such as FPGAs, provides a programmable substrate onto which descriptions of circuits can be loaded and executed at very high speeds. Because they are able to provide an attractive balance between performance, cost, and flexibility, many critical embedded systems make use of FPGAs as their primary source of computation. Their circuit-level flexibility allows system functionality to be updated arbitrarily and remotely. For example, the aerospace industry relies on FPGAs to control everything from satellites to the Mars Rover.

FPGAs lie along a continuum between general-purpose processors and applicationspecific integrated circuits (ASICs). They provide both high-performance and welldefined timing behavior, but they do not require the costly fabrication of custom chips.

While general purpose processors can execute any program, this generality comes at

the cost of serialized execution. On the other hand, ASICs can achieve impressive

parallelism, but their function is literally hard wired into the device. The power of reconfigurable systems lies in their ability to flexibly customize an implementation down

at the level of individual bits and logic gates without requiring a custom piece of silicon. This can often result in performance improvements on the order of magnitude as

compared to, per unit silicon, a similar microprocessor [24, 14]. FPGA technology is

now the leading design driver for almost every single foundry. In fact it is estimated that

in 2005 alone there were over 80,000 different commercial FPGA design starts [67].

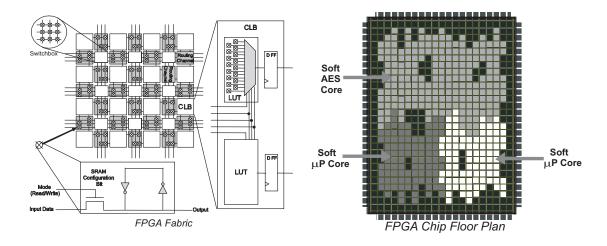

Figure 1.1: A simplified representation of an FPGA fabric is on the left. Configurable Logic Blocks (CLBs) perform logic level computation using Lookup Tables (LUTs) for bit manipulations and flipflops for storage. The switch boxes and routing channels provide connections between the CLBs. SRAM configuration bits are used throughout the FPGA (e.g., to program the logical function of the LUTs and connect a segment in one routing channel to a segment in an adjacent routing channel). The FPGA floor plan on the right illustratively shows a physical layout of FPGA after routing.

Figure 1.1 provides a simplified diagram of the modern FPGA architecture. FP-GAs have very regular gate level patterns which differs from ASIC realization. Here the CLBs (configurable with LUT) are the basic logic/computing units. By connecting the CLBs using the interconnection resources (switchboxes and routing channels), an FPGA can be programmed to perform virtually any computation. It is worthwhile to note the tremendous flexibility the FPGA architecture provides to the designers. They have the capability to implement a wide variety of custom circuits, ranging from simple

adder/multiplier or multiple instances of them, to an entire computational function (e.g. digital filter, video codec), or even a complete CPU core (e.g. PowerPC 4507). This is very appealing; however, it also brings difficult questions regarding how to effectively use such flexibility. For example, for a given application and a known FPGA platform, what is the optimal configuration that achieves the best timing performance? Additionally, what is the impact on the system configuration (such as the number of adders and multipliers) if the requirements are relaxed? Moreover, is there a systematic method to help the designers explore the huge design decision space created by such increased flexibility?

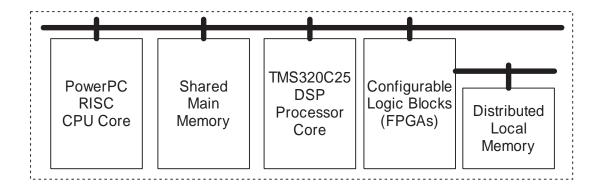

Similar questions exist beyond the fine granularity level and the scope of pure FPGA-based platforms. In order to find cost effective ways to get the desired performance and maximize uses of resources, we often find designs that compose a hybrid technologies in today's systems. The most well-known example is the hardware/software co-design problem, where a system is composed of a general purpose CPU and a hardware-based computing resource (either ASIC or FPGA). More generally, a hybrid system can be organized to have *n* computing units with different capabilities and characteristics. How to assist the designer to effectively partition and distribute the computing tasks of an application over various computing units remains a system level challenge.

In general, as the complexity of digital systems increases, so does the complexity of these underlying EDA problems. To make it more difficult, many of these problems

are  $\mathcal{N}$ P-hard, which implies that finding optimal polynomial time algorithms for these problems are very unlikely. Due to this fact, almost all existing EDA systems apply heuristics to some extent. These heuristics were likely very successful and effective when they were invented. However, as the complexity of the problems increases, the conventional heuristic methods may fail in handling today's larger problems effectively. To face these challenges, we must look towards new optimization methods, rather than simply perform iterative improvements on existing techniques.

### 1.2 Research Overview

My dissertation research work is focused on constructing effective heuristic algorithms for solving difficult and fundamental design optimization problems. More specifically, the research focuses on devising new design automation algorithms based on the Ant Colony metaheuristics or Ant Colony Optimization (ACO) techniques. The ACO method is a relatively new meta-heuristic approach inspired by the ecological study of social insects (ants) and can be classified as a population based, self-organized meta-heuristic method; it was originally formulated to solve traditional  $\mathcal{NP}$ -hard combinatory problems in late 1990's and has been since successfully applied to solve a number of traditional  $\mathcal{NP}$ -hard combinatory problems.

ACO distinguishes itself from other conventional meta-heuristic methods (e.g. simulated annealing and genetic algorithms) with the following advantages:

• It formulates an optimization problem as a collaborative search process;

- It provides an effective way to combine global search experience with problem specific heuristics using pheromone sharing;

- It utilizes indirect communication in learning and employs positive feedback to achieve fast convergence;

- It offers a new and powerful way for solving optimization problems modeled as a graph, which is often the underlying model for various architectural problems.

Similar to other versatile meta-heuristic methods, such as Stimulated Annealing(SA), Genetic Algorithm (GA) and A\* algorithm, it is possible to apply the Ant Colony metaheuristics to a slew of problems. However, careful attention has to be paid to consider the specific characteristics of the problem at hand and effectively integrate them in the final algorithms. In our study, we have selected to focus on three fundamental EDA problems, namely the system level partitioning problem, the operation scheduling problem and the design space exploration problem. These problems cover a good range of design granularity and are traditionally considered to be very difficult. We believe that these problems provide a good set of test cases for verifying the effectiveness of our methods. By addressing these problems with concretely constructed algorithms using Ant Colony metaheuristics, we hope to enrich and make contributions to the future system design methodologies.

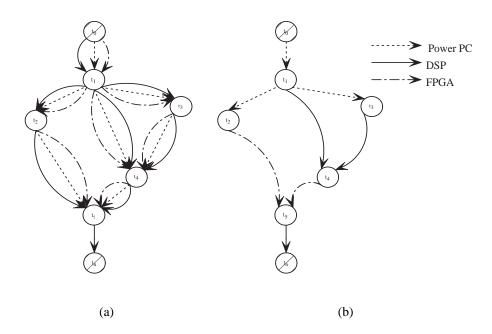

As our first effort of applying the Ant Colony metaheuristics, we formulate new algorithms to address the system level task partitioning problem [102, 103, 105]. This problem is a fundamental  $\mathcal{NP}$ -hard challenge in a number of fields including high-level

system synthesis, parallel and distributed computing, and hardware/software co-design. It attempts to map application tasks onto multiple system resources w.r.t. the latency, hardware cost, power and other performance metrics. We construct a novel ACO-based algorithm to address this problem by introducing the Augmented Task Graph model. The concept can be easily extended to handle a variety of system requirements, including truly addressing the multi-way partitioning problem. The proposed algorithm consistently provides near optimal partitioning results on modestly-sized tested samples with very minor computational cost. For larger size problems, our algorithm scales well and achieves better solutions than the popularly used simulated annealing approach with substantially less execution time. Furthermore, we propose a hybrid approach that combines the ACO and simulated annealing together. This hybrid method leverages the complementary behaviors of the two algorithms and yields even better results than using them individually.

Operation scheduling is another fundamental architectural synthesis problem. An inappropriate scheduling of the operations will fail to exploit the full potential of the system. High quality scheduling solutions have direct impact in a number of different fields, such as compiler design for superscalar and VLIW microprocessors, distributed clustering computation architectures and hardware synthesis of ASICs and FPGAs. In our work, we introduce two novel algorithms [104, 99] using the ACO approach for the timing and resource constrained scheduling problems. We compile a comprehensive testing benchmark set (ExpressDFG) to verify the effectiveness and efficiency of the

proposed algorithms. For timing constrained scheduling, our algorithm achieves better results compared to force-directed scheduling on almost all the testing cases attaining a 19.5% reduction of resources. For resource constrained scheduling, our algorithm outperforms a number of list scheduling heuristics with better stability, and generates up to a 14.7% performance improvement. Our algorithms outperform the simulated annealing method for both scheduling problems in terms of quality, compute time and stability.

Finally, we look into the Design Space Exploration (DSE) problem, which tries to generate Pareto optimal tradeoffs among different system configurations. DSE is another critical challenge of high level synthesis. In practice, it is often addressed through ad-hoc probing of the solution space. This is not only time consuming but also very dependent on the designers experience. We propose a novel design exploration method that exploits the duality of the time and resource constrained scheduling problems [100, 101]. Our exploration automatically constructs a high quality time/area tradeoff curve in a fast, effective manner. In order to fully benefit from the duality attribute, we leverage the ACO-based optimization methods to solve both scheduling problems. We switch between these two algorithms to quickly traverse the design space. Compared with using force directed scheduling exhaustively at every time step, our approach provides a significant improvement on solution quality (average 17.3% reduction of resource counts) with similar run time on a comprehensive benchmark suite. It also scales well over different applications and problem sizes.

To summarize our research work, we focus on the essential algorithmic issues of applying Ant Colony metaheuristics to solve fundamental architectural design problems. We have successfully devised a series of algorithms for a number of problems across different levels of design granularity and achieved very promising results. We believe that Ant Colony metaheuristic is a framework of great potential in solving architectural design problems, and is not limited to the ones we studied. Moreover, we have developed a software tool, named CODES, to provide a uniform implementation for applying the ACO method to these architectural problems. To our best knowledge, our work is the first to introduce the Ant Colony metaheuristics to the architectural design field.

## 1.3 Organization of Dissertation

The dissertation is organized as follows: In Chapter 2, we give a review on the Ant Colony metaheuristic method with discussion on its characteristics. We present our work on applying the Ant Colony metaheuristic to solve system partitioning problem by introducing the Augmented Task Graph as the basic model in handling *n*-way partitioning problem in Chapter 3. In Chapter 4, we discuss how to solve timing and resource constrained operation scheduling problems. Also in this chapter, we will introduce the ExpressDFG benchmark suit we constructed. The same benchmark set will also be used in evaluating the design space exploration algorithm. We look into the parameter sensitivity issues experimentally. We introduce the duality based design

space exploration approach in Chapter 5. To lay the theoretical foundation, we will first prove an important theorem regarding duality between timing and resource constrained scheduling. Moreover, we will explain why ACO-based scheduling algorithms are favored in the proposed exploration framework. We conclude with Chapter 6.

# Chapter 2

## **Ant Colony Metaheuristic**

## 2.1 Nature Inspired Metaheuristics

As we have indicated in the previous chapter, fundamental architectural decisions often rely on solving  $\mathcal{NP}$ -hard combinatory optimization problems. With increasing complexity of these problems in today's applications, it becomes impossible to obtain the exact optimal solutions within a reasonable computation, and we have to use heuristic methods to hopefully obtain close-to-optimal results. One important approach for doing so is to select and utilize a metaheuristic method.

A metaheuristic is a heuristic method for solving a very general class of computational problems. It attempts to provide an efficient framework which combines user given black-box procedures. Such procedures are usually application specific heuristics themselves. The name combines the Greek prefix "meta" ("beyond", here in the

sense of "higher level") and "heuristic" (from ευρισκειν, heuriskein, "to find"). Metaheuristics are generally applied to problems for which there is no satisfactory problemspecific algorithm or heuristic; or when it is not practical to implement such a method. Most commonly used metaheuristics are targeted to combinatorial optimization problems.

The simplest and most well known metaheuristic perhaps is the *Hill Climbing* method [82]. It is an optimization technique that belongs to the family of *local search* algorithms. The relative ease in implementation makes it a very popular first choice. However, this a simple method often fails to provide high quality results since it can easily get trapped within local minima.

In the past decades, a series of metaheuristic methods have been devised and successfully applied to a wide range of applications. It is interesting to notice that the best performing metaheuristics are almost inspired by nature.

Simulated annealing is a generic probabilistic meta-algorithm for finding global optima in large search space [56]. It was inspired by the annealing process in metallurgy, a technique involving heating and controlled cooling of a material to increase the size of its crystals and reduce their defects. The heat causes the atoms to move from their initial positions (a local minimum of the internal energy) and wander randomly through states of higher energy; the slow cooling gives them a chance of finding configurations with lower internal energy than the initial one.

Genetic algorithms use techniques inspired by evolutionary biology such as inheri-

tance, mutation, selection, and crossover (also called recombination) [70]. They essentially solve the problems under consideration by simulating the evolutionary process, in which a population of abstract representations (called *chromosomes* or the genotype or the genome) of candidate solutions (called individuals, creatures, or phenotypes) evolves toward better solutions.

**Artificial neural networks** borrow the concept from how the human brain processes information by using an interconnected group of artificial neurons [1]. In solving an optimization problem, artificial neural networks use a mathematical model or computational model for information processing based on a connectionist approach, in which each processing unit is to simulate a individual neuron.

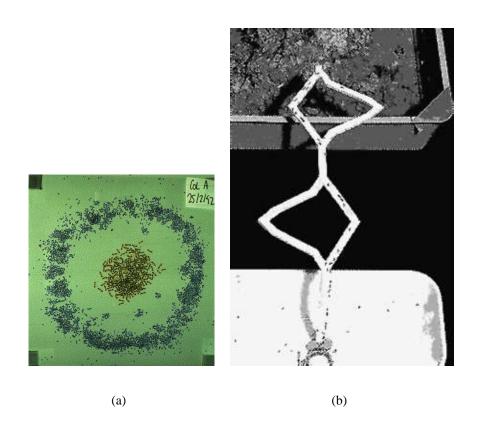

The Ant Colony Metaheuristic is a relatively new addition to the family of nature inspired algorithms for solving  $\mathcal{N}P$ -hard combinatory problems. Also known as Ant Colony Optimization (ACO) or Ant System (AS) algorithm<sup>1</sup> and originally introduced by Dorigo *et al.* [28] in 1996, it is a cooperative heuristic searching algorithm inspired by the ethological study on the behavior of ants. Figure 2.1(a) shows a laboratory nest constructed by a Leptothorax ant colony. The shown laboratory nest is made of two microscope slides separated by four 1mm thick cardboard pillars, one pillar at each corner. It closely approximates the rock crevices these ant colonies choose as nest sites in nature and facilitates easy observation on the ant behaviors. The blue dots are colored sand blocks from a pile provided outside the nest site that the ants have used

<sup>&</sup>lt;sup>1</sup>In the rest of the discussion, we may use these terms interchangeably if not otherwise indicated

**Figure 2.1:** (a) A laboratory nest of a Leptothorax ant colony; (b) Experiment settings used in [25].

for building a perimeter wall of the nest.

It was observed [25] that ants – who lack sophisticated vision – could manage to establish the optimal path between their colony and the food source within a very short period of time. This is done by an indirect communication known as stigmergy via the chemical substance, or *pheromone*, left by the ants on the paths. Though any single ant moves essentially at random, it will make a decision on its direction biased on the "strength" of the pheromone trails that lie before it, where a higher amount of pheromone hints a better path. As an ant traverses a path, it reinforces that path with its own pheromone. A collective autocatalytic behavior emerges as more ants will choose the shortest trails, which in turn creates an even larger amount of pheromone on those short trails, which makes those short trails more likely to be chosen by future ants. The experiment setup for the study done in [25] is shown in Figure 2.1(b), in which the ants converge to the shortest path between their nest and food source amongst four possible alternatives. The ACO algorithm is inspired by such observation. It is a population based approach where a collection of agents cooperate together to explore the search space. They communicate via a mechanism imitating the pheromone trails. The algorithm can be characterized by the following steps:

- 1. The optimization problem is formulated as a search problem on a graph;

- A certain number of ants are released onto the graph. Each individual ant traverses the search space to create its solution based on the distributed pheromone trails and local heuristics;

- 3. The pheromone trails are updated based on the solutions found by the ants;

- If predefined stopping conditions are not met, then repeat the first two steps;

Otherwise, report the best solution found.

### 2.2 ACO for Travel Salesman Problem

One of the first problems to which ACO was successfully applied was the Traveling Salesman Problem (TSP) [28], for which it gave competitive results compared to traditional methods.

The objective of TSP is to find a Hamiltonian path for the given graph that gives the minimal length. More specifically, a TSP can be represented by a complete weighted directed graph G = (V, E, d) where  $V = \{1, 2, ..., n\}$  is a set of vertexes or cities,  $E = \{(i, j) | (i, j) \in V \times V\}$  is a set of edges, and d is a weight function which associates a numeric weight  $d_{ij}$  for each edge (i, j) in E. This weight is naturally interpreted as the distance between city i and j in TSP. The objective is to find a Hamiltonian path for G which gives the minimal length.

In order to solve the TSP problem, ACO associates a pheromone trail for each edge in the graph. The pheromone indicates the attractiveness of the edge and serves as a global distributed heuristic. For each iteration, a certain number of ants are released randomly onto the nodes of the graph. An individual ant will choose the next node of the tour according to a probability that favors a decision of the edges that possesses

higher volume of pheromone. Upon finishing of each iteration, the pheromone on the edges is updated. Two important operations are taken in this pheromone updating process. First, the pheromone will evaporate, and secondly the pheromone on a certain edge is reinforced according to the quality of the tours in which that edge is included. The evaporation operation is necessary for ACO to effectively avoid local minima and diversify future exploration onto different parts of the search space, while the reinforcement operation ensures that frequently used edges and edges contained in better tours receive a higher volume of pheromone, which will have better chance to be selected in the future iterations of the algorithm. The above process is repeated multiple times until a certain stopping condition is reached. The best result found by the algorithm is reported as the final solution.

The algorithm associates a pheromone trail  $\tau_{ij}$  for each edge (i,j) in E. It indicates the attractiveness of the edge and serves as a global distributed heuristic. Initially,  $\tau_{ij}$  is set with some fixed value  $\tau_0$ . For each iteration, m ants are released randomly on the cities, and each starts to construct a tour. Every ant will have memory about the cities it has visited so far in order to guarantee the constructed tour is a Hamiltonian path. If at step t the ant is at city i, the ant chooses the next city j probabilistically according to a probability:

$$\mathsf{p}_{ij} = \begin{cases} \frac{\tau_{ij}(t)^{\alpha} \cdot \eta_{ij}^{\beta}}{\sum_{k} (\tau_{ik}^{\alpha}(t) \cdot \eta_{ik}^{\beta})} & \text{if is } j \text{ not visited} \\ 0 & \text{otherwise} \end{cases}$$

(2.1)

where edges (i,k) are all the allowed moves from i,  $\eta_{ik}$  is a local heuristic which is defined as the inverse of  $d_{ij}$ ,  $\alpha$  and  $\beta$  are parameters to control the relative influence of

the distributed global heuristic  $\tau_{ik}$  and local heuristic  $\eta_{ik}$ . Intuitively, the ant favors a decision on a edge that possesses higher volume of pheromone trail and better distance cost. Upon finishing of each iteration, the pheromone trail is updated according to the tours in which it is included. In the mean time, a certain amount of the it will evaporate. More specifically, we have:

$$\tau_{ij}(t) = \rho \cdot \tau_{ij}(t) + \sum_{k=1}^{m} \Delta \tau_{ij}^{k}(t) \qquad \text{where } 0 < \rho < 1.$$

(2.2)

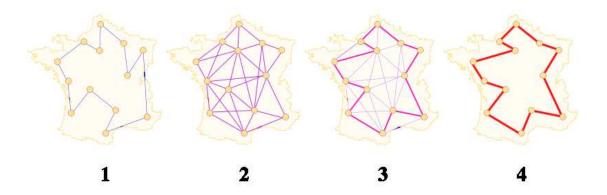

Here  $\rho$  is the evaporation ratio, and  $\Delta \tau_{ij}^k = Q/L_k$  if edge (i,j) is included in the tour ant k constructed, otherwise  $\Delta \tau_{ij}^k = 0$ . Q is a fixed constant to control the delivery rate of the pheromone, while  $L_k$  is the tour length for ant k. Two important operations are taken in this pheromone trail updating process. The evaporation operation is necessary for AS to be effective and diversified to explore different parts of the search space, while the reinforcement operation ensures that frequently used edges and edges contained in better tours receive a higher volume of pheromone and will have better chance to be selected in the future iterations of the algorithm. The above process is repeated multiple times until certain ending condition is reached. The best result found by the algorithm is reported. Figure 2.2 gives a visual illustration on how the above process works.

# **2.3** ACO for Other Combinatory Problems

When compared with existing algorithms over a set of difficult testing cases of the TSP, the ACO method achieved very competitive results [28] either on result quality

**Figure 2.2:** An illustration on how ACO-TSP works.

- (1) Single ant constructs a solution; (2) Multiple solutions are constructed by all the ants individually;

- (3) The pheromone trails adaptively adjust their values during the iterations; (4) The optimal solution emerges as the search learns from its experience.

or the computing time. Motivated by this success, researchers have since formulated ACO methods for a variety of traditional  $\mathcal{NP}$ -hard problems. These problems include the maximum clique problem [34], the quadratic assignment problem [37], the graph coloring problem [22], the shortest common super-sequence problem [61, 71], and the multiple knapsack problem [35]. ACO also has been applied to practical problems such as the vehicle routing problem [36], data mining [77] and network routing problem [83]. More recently, ACO approach was also successfully for bioinformatics application [87]. Table 2.1 gives a brief summary on the problems that ACO algorithms have been devised and related results.

| Problem                                 | Performance                         |

|-----------------------------------------|-------------------------------------|

| Traveling salesman                      | state-of-the-art / good performance |

| Quadratic assignment                    | state-of-the-art / good performance |

| Job-Shop Scheduling                     | state-of-the-art / good performance |

| Vehicle routing                         | state-of-the-art / good performance |

| Sequential ordering                     | state-of-the-art performance        |

| Shortest common supersequence           | good results                        |

| Graph coloring and frequency assignment | good results                        |

| Bin packing                             | state-of-the-art performance        |

| Constraint satisfaction                 | good performance                    |

| Multi-knapsack                          | poor performance                    |

| Timetabling                             | good performance                    |

| Optical network routing                 | promising performance               |

| Set covering and partitioning           | good performance                    |

| Parallel implementations and models     | good parallelization efficiency     |

| Routing in telecommunications networks  | state-of-the-art performance        |

| Protein Folding                         | state-of-the-art performance        |

**Table 2.1:** Applications of ACO method and their qualitative performance

# 2.4 Convergency of ACO Method

The convergence property of the ACO approach was investigated in [44, 46]. It was shown that ACO with a time-dependent evaporation factor or a time-dependent lower pheromone bound converges to an optimal solution with probability exactly one. The result enhanced the work presented in [45, 43, 91] for ACO algorithms to the strength of the well-known convergence property of the Simulated Annealing meta-heuristic. As in Simulated Annealing, it turns out that a convergence guarantee can be obtained

by a suitable speed of "cooling" (i.e., reduction of the influence of randomness). First, in the basic ACO formulation, the geometric pheromone decrement caused by constant evaporation factor on not reinforced arcs is too fast and leads (in general) to premature convergence to suboptimal solutions. On the other hand, introducing a fixed lower pheromone bound stops cooling at some point and leads to random-search-like behavior without convergence. In between lies a compromise of allowing pheromone trails to tend to zero, but slower than geometrically. This can be achieved either by decreasing evaporation factors, or else by "slowly" decreasing lower pheromone bounds. In a certain window of the cooling speed, we get convergence to the optimal solution with probability of one.

However, it is worth noting that that the theoretical cooling speeds indicated in [44] are also the most efficient ones, where efficiency is measured by the average runtime required to find a solution of a sufficiently good quality (say, only  $\rho$ % worse than the best solution with some pre-defined  $\rho$ ). In the typical area of application for ACO, i.e. the area of  $\mathcal{NP}$ -complete combinatorial optimization problems, we cannot expect to obtain an algorithm providing optimal solutions in a short computation time. Again, as in Simulated Annealing, it might turn out that faster cooling than indicated by the theoretical scheme is advantageous for finite-time computing – that is for getting quick convergence, it may be worthwhile to pay the price of convergence to suboptimal solutions. However, experimental studies with slightly decreasing evaporation factors or lower pheromone bounds falling slightly slower than geometrically might be interest-

ing, especially for applications where the user is willing to invest a high amount of computation time for obtaining excellent solution quality. In addition to the (so-called "elitist") pheromone update mechanisms investigated in the paper, the author also suggests computational experiments with decreasing evaporation factors and/or decreasing lower pheromone bounds for other empirically successful update mechanisms, such as the rank-based update rule introduced by Bullheimer, Hartl and Strauss [15]. It would not be a surprise if some moderate form of retarding the cooling process could, in a considerable number of cases, be able to further improve the performance of present ACO implementations.

## 2.5 MAX-MIN Ant System (MMAS)

Premature convergence to local minima is a critical algorithmic issue that can be experienced by many heuristic optimization algorithms. As we have discussed in the previous section, though it was shown [44] that ACO with a time-dependent evaporation factor or a time-dependent lower pheromone bound converges to an optimal solution with probability of exactly one, it failed in providing any constructive approach. Balancing exploration and exploitation is not trivial in these algorithms, especially for algorithms that use positive feedback such as ACO.

The MAX-MIN Ant System (MMAS) [92] is one framework to provide such balance in an adaptive manner. It is built upon the original ACO algorithm and is specifically designed to address the premature convergence problem. It improves the original

ACO by providing dynamically evolving bounds on the pheromone trails such that the heuristic value is always within a limit to that of the best path. As a result, all possible paths will have a non-trivial probability of being selected and thus it encourages broader exploration of the search space.

More specifically, MMAS forces the pheromone trails to be limited within evolving bounds, that is for iteration t,  $\tau_{min}(t) \leq \tau_{ij}(t) \leq \tau_{max}(t)$ . If we use f to denote the cost function of a specific solution S, the upper bound  $\tau_{max}$  [92] is shown in (2.3). Here  $S^{gb}(\cdot)$  represents the global best solution found so far in all iterations.

$$\tau_{max}(t) = \frac{1}{1 - \rho} \frac{1}{f(S^{gb}(t - 1))}$$

(2.3)

The lower bound is defined as (2.4):

$$\tau_{min}(t) = \frac{\tau_{max}(t)(1 - \sqrt[n]{p_{best}})}{(avg - 1)\sqrt[n]{p_{best}}}$$

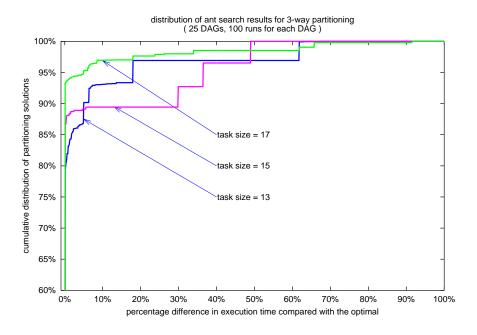

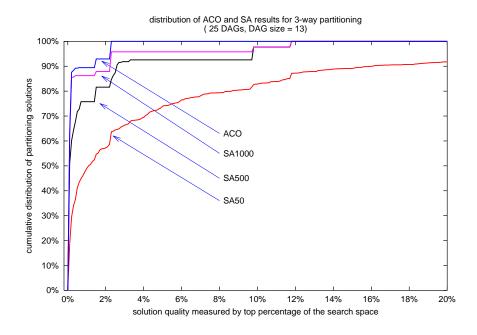

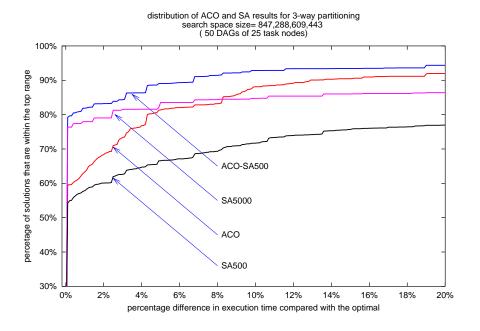

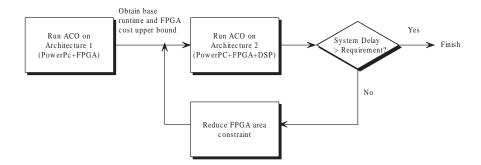

(2.4)