#### CSE140L: Components and Design Techniques for Digital Systems Lab

Introduction

**Tajana Simunic Rosing**

#### Welcome to CSE 140L!

- Instructor: Tajana Simunic Rosing

- Email: tajana@ucsd.edu; please put CSE140L in the subject line

- Ph. 858 534-4868

- Office Hours: W 11:00-12:00pm; Th 11:30-12:30pm; CSE 2118

- Instructor's Assistant: Sheila Manalo

- Email: shmanalo@ucsd.edu

- Phone: (858) 534-8873

- TA: Gautham Reddy Email:greddy@ucsd.edu TA office hrs: Tu/Fri?

- Class Website:

- <u>http://www.cse.ucsd.edu/classes/wi10/cse140L/</u>

- Grades: <u>http://webct.ucsd.edu</u>

# **Course Description**

- Prerequisites:

- CSE 20 or Math 15A, and CSE 30.

- CSE 140 must be taken concurrently

- Objective:

- Introduce digital components and system design concepts through hands-on experience in a lab

- Grading

- Labs (4): 70%

- First two labs will use simulation only, the 2<sup>nd</sup> two labs will use Xilinx HW

- Schedule for lab access; need to schedule a demo to TA by lab due date

- Go to Robin Knox [rsknox@cs.ucsd.edu] office in CSE 2248 to program your student ID for access to CSE 3219

- Monday-Thursday 10-12:30 and 2:00-4:00

- Exam: 30%

- Regrade requests: turn in a written request at the end of the class where your work is returned

## **Textbook and Recommended Readings**

#### Required textbook:

Contemporary Logic Design by R. Katz & G. Borriello

- Recommended textbook:

- Digital Design by F. Vahid

• Lecture slides are derived from the slides designed for both books

## Software and Hardware we will use

- Freely available in CSE 3219 lab:

- Xilinx Virtex-II Pro Development System (XUPV2P)

http://www.xilinx.com/univ/xupv2p.html

- PC in the lab already have ISE tools installed.

You can program boards in the lab only!

- You can download on your own PC Webpack tools to implement and test your design; this is all that will be needed for the first two labs.

www.xilinx.com/ise/logic\_design\_prod/webpack.htm

# Outline

- Introduction to Xilinx board & tools

- Transistors

- How they work

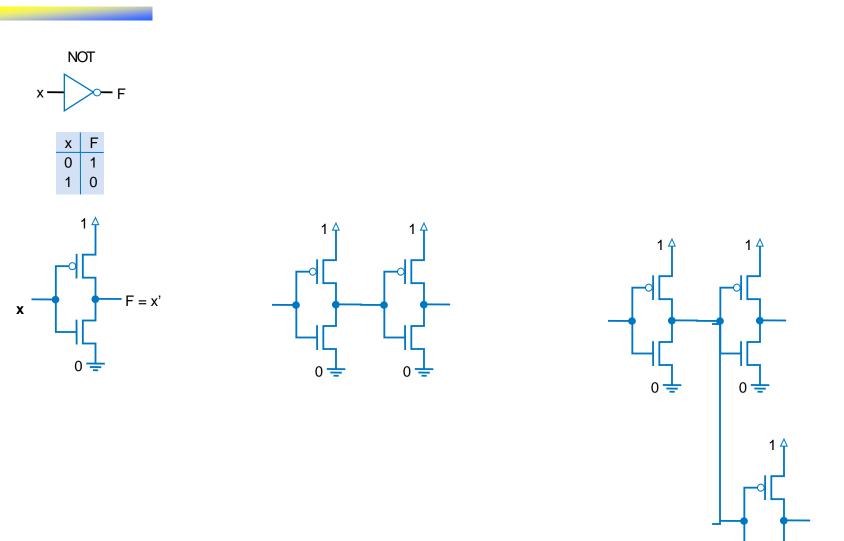

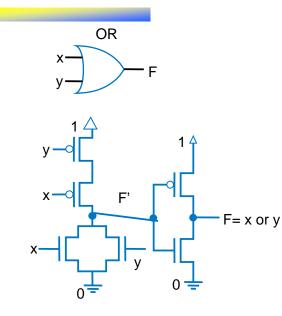

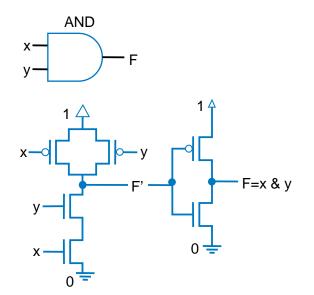

- How to build basic gates out of transistors

- How to evaluate delay

- Pass gates

- Muxes

#### Quick intro to Xilinx board and tools

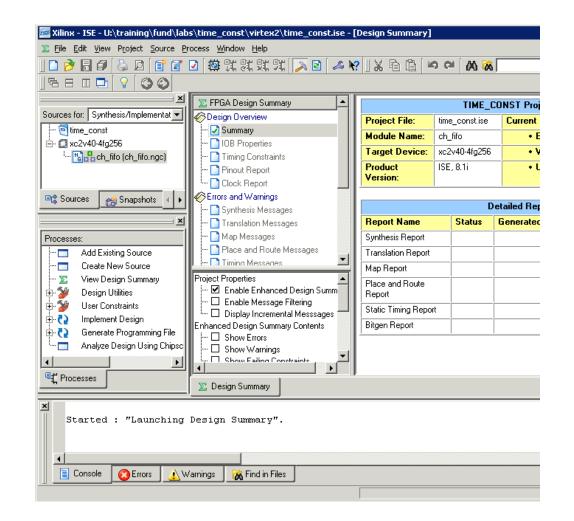

# **ISE Project Navigator**

- Built around the Xilinx design flow

- Access to synthesis and schematic tools

- Including thirdparty synthesis tools

- Implement your design with a simple double-click

- Fine-tune with easy-to-access software options

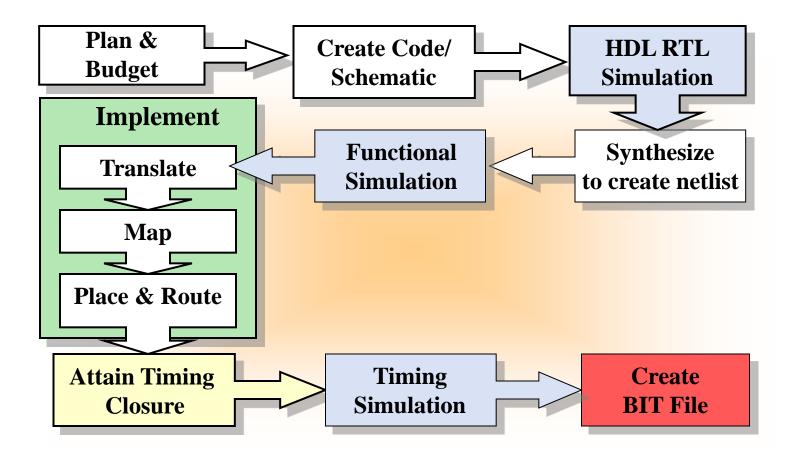

#### Xilinx Design Flow

Combinational circuit building blocks: Transistors, gates and timing

**Tajana Simunic Rosing**

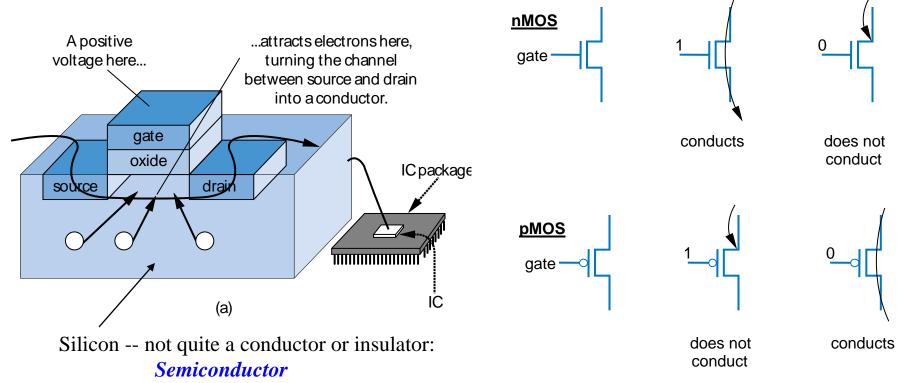

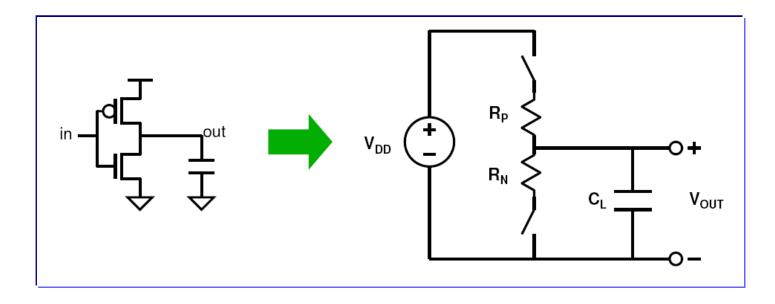

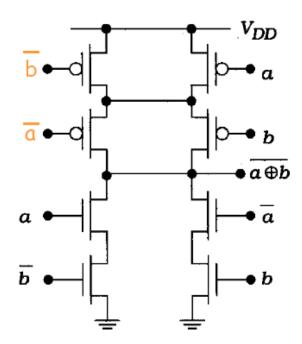

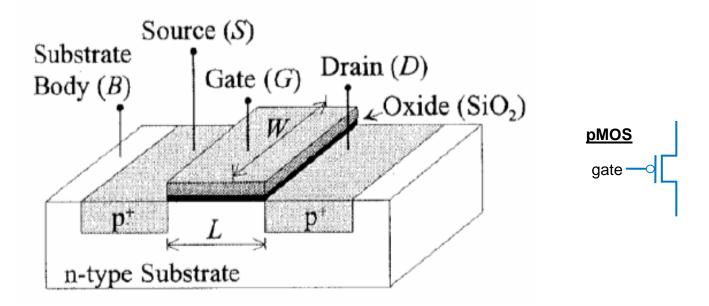

# The CMOS Circuit

- CMOS circuit

- Consists of N and PMOS transistors

- Both N and PMOS operate similar to basic switches

## Charge/discharge in CMOS

- Calculate on resistance

- Calculate capacitance of the gates circuit is driving

- Get RC delay & use it as an estimate of circuit delay

V<sub>out</sub> = V<sub>dd</sub> (1- e<sup>-t/RpC</sup>)

- Rp ~ 2Rn

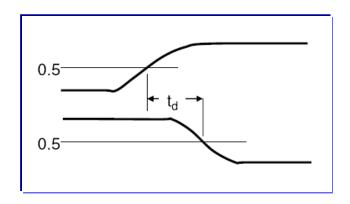

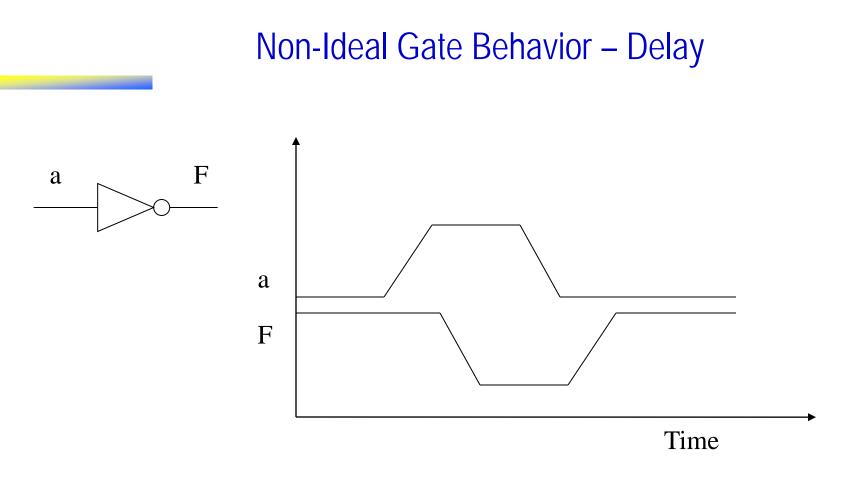

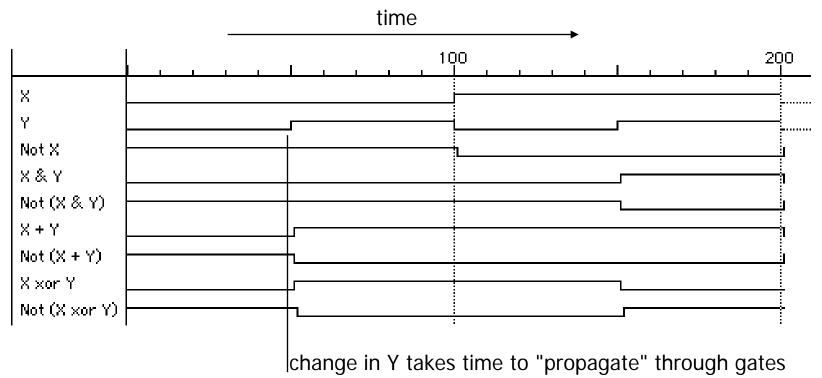

- Real gates don't respond immediately to input changes

- Rise/fall time

- Delay

- Pulse width

#### Waveform view of logic functions

- Just a sideways truth table

- but note how edges don't line up exactly

- it takes time for a gate to switch its output!

## Timing analysis: Inverter

16

0 🚽

# Timing analysis in gates

### More complex gates

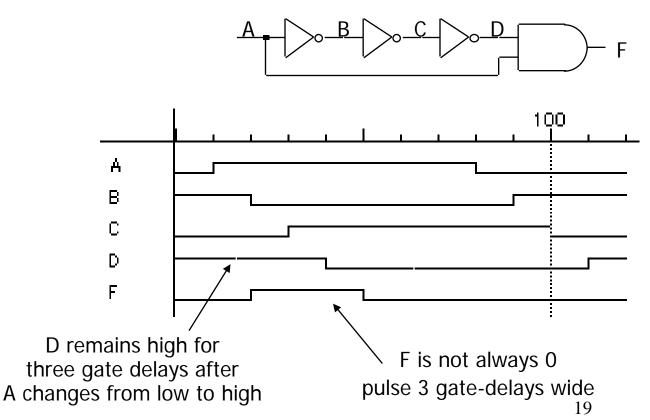

#### When is non-ideal gate behavior a good thing?

- Can be useful pulse shaping circuits

- Can be a problem incorrect circuit operation

- Example: pulse shaping circuit

- $A' \bullet A = 0$

- delays matter

CSE140: Components and Design Techniques for Digital Systems

Muxes and demuxes

**Tajana Simunic Rosing**

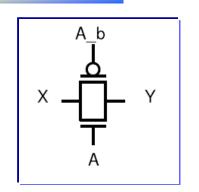

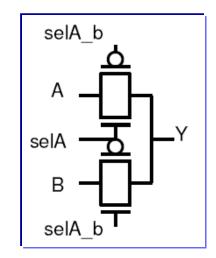

#### Pass transistor – Mux building block

Connects X & Y when A=1, else X & Y disconnected

A\_b = not(A)

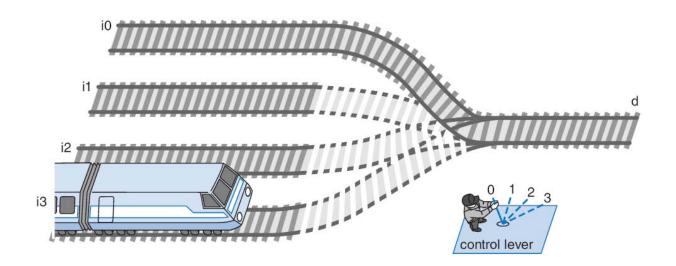

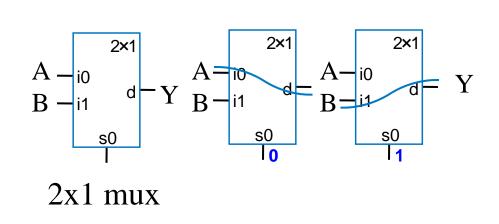

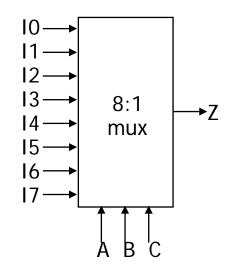

# Multiplexor (Mux)

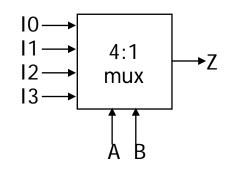

- Mux routes one of its N data inputs to its one output, based on binary value of select inputs

- 4 input mux → needs 2 select inputs to indicate which input to route through

- 8 input mux  $\rightarrow$  3 select inputs

- N inputs  $\rightarrow \log_2(N)$  selects

## Mux Internal Design

- Selects input to connect to Y

- selA == 1: connects A to Y

- selB == 1: connects B to Y

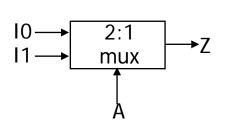

#### Multiplexers/selectors

- 2:1 mux:  $Z = A'I_0 + AI_1$

- 4:1 mux:  $Z = A'B'I_0 + A'BI_1 + AB'I_2 + ABI_3$

- 8:1 mux:  $Z = A'B'C'I_0 + A'B'CI_1 + A'BC'I_2 + A'BCI_3 + AB'C'I_4 + AB'CI_5 + ABC'I_6 + ABCI_7$

• In general:

$$Z = \sum_{k=0}^{2^n} (m_k I_k)$$

– in minterm shorthand form for a  $2^{n}$ :1 Mux

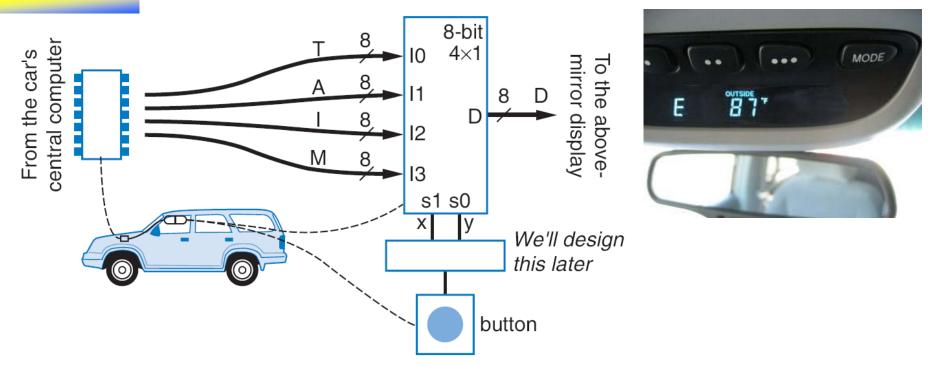

## N-bit Mux Example

- Four possible display items

- Temperature (T), Average miles-per-gallon (A), Instantaneous mpg (I), and Miles remaining (M) -- each is 8-bits wide

- Choose which to display using two inputs x and y

- Use 8-bit 4x1 mux

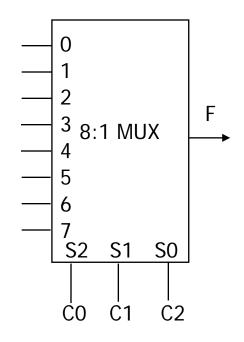

## Multiplexers as general-purpose logic

- A 2<sup>n-1</sup>:1 multiplexer can implement any function of n variables

- with n-1 variables used as control inputs and

- the data inputs tied to the last variable or its complement

- Example: F(A,B,C) = ABC + ABC'+A'BC+AB'C

#### Mux example: Logical function unit

| <u>C0</u> | C1 | C2 | Function | Comments     |

|-----------|----|----|----------|--------------|

| 0         | 0  | 0  | 1        | always 1     |

| 0         | 0  | 1  | A + B    | logical OR   |

| 0         | 1  | 0  | (A • B)' | logical NAND |

| 0         | 1  | 1  | A xor B  | logical xor  |

| 1         | 0  | 0  | A xnor B | logical xnor |

| 1         | 0  | 1  | A • B    | logical AND  |

| 1         | 1  | 0  | (A + B)' | logical NOR  |

| 1         | 1  | 1  | 0        | always 0     |

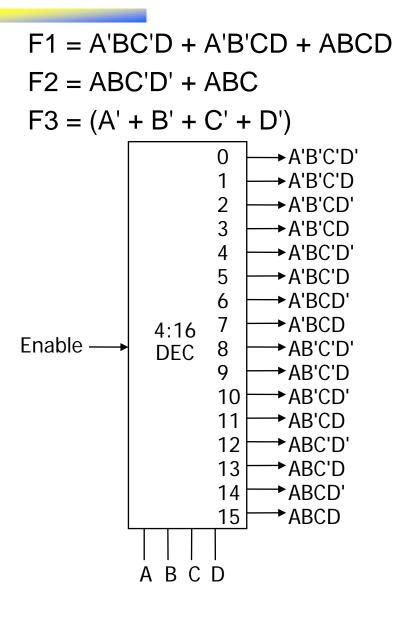

#### Demultiplexers/decoders

- Decoders/demultiplexers: general concept

- single data input, n control inputs, 2<sup>n</sup> outputs

- control inputs (called "selects" (S)) represent binary index of output to which the input is connected

- data input usually called "enable" (G)

| 00                              | <u>Deco</u><br>= G<br>= G | • S        | 1 |          |

|---------------------------------|---------------------------|------------|---|----------|

| $\frac{2:4}{00} = 01 = 02 = 02$ | G•<br>G•                  | S1′<br>S1′ | • | S0<br>S0 |

| 02 = 03 =                       | _                         | -          |   |          |

| 3:8 Decoder:     |       |           |  |  |  |  |

|------------------|-------|-----------|--|--|--|--|

| 00 = G •         | S2′ • | S1' • S0' |  |  |  |  |

| 01 = G ●         | S2′ ● | S1' • S0  |  |  |  |  |

| O2 = G ●         | S2′ ● | S1 • S0'  |  |  |  |  |

| $O3 = G \bullet$ | S2′ ● | S1 • S0   |  |  |  |  |

| $O4 = G \bullet$ | S2 •  | S1' • S0' |  |  |  |  |

| O5 = G ●         | S2 •  | S1' • S0  |  |  |  |  |

| 06 = G ●         | S2 •  | S1 • S0'  |  |  |  |  |

| O7 = G ●         | S2 •  | S1 • S0   |  |  |  |  |

## Gate level implementation of demultiplexers

- 1:2 decoders

- $\frac{1:2 \text{ Decoder:}}{00 = G \bullet S'}$  $01 = G \bullet S$

- 2:4 decoders

$\begin{array}{r} 2:4 \ Decoder:\\ \hline 00 = G \bullet S1' \bullet S0'\\ 01 = G \bullet S1' \bullet S0\\ 02 = G \bullet S1 \bullet S0'\\ 03 = G \bullet S1 \bullet S0\end{array}$

Demultiplexers as general-purpose logic (cont'd)

#### What we've covered thus far

- Xilinx Virtex II Pro board and tools

- Transistor design

- Building basic gates from CMOS

- Delay estimates

- Pass transistors

- Muxes

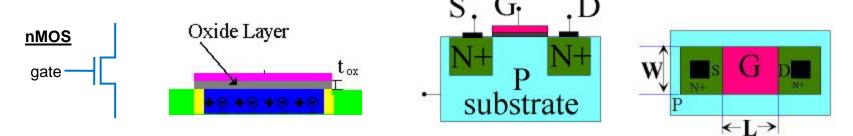

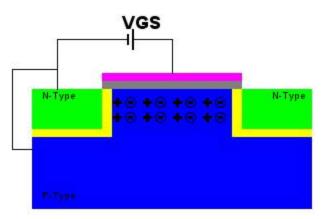

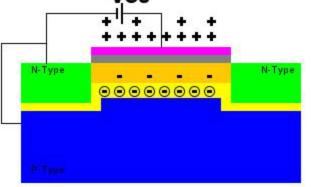

## N-MOS Tutorial – channel formation

The Semiconductor-Oxide-Metal Combination in the Gate is effectively a <u>Parallel Plate Capacitor</u>

• Vgs = 0 -> lots of positive charge in p-type material, no current

Source: <a href="http://www.netsoc.tcd.ie/~mcgettrs/hvmenu/tutorials/TOCcmostran.htm">http://www.netsoc.tcd.ie/~mcgettrs/hvmenu/tutorials/TOCcmostran.htm</a>

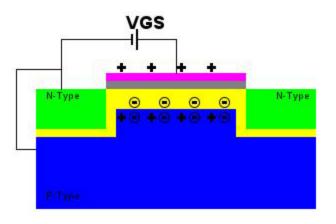

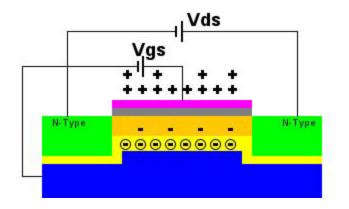

# N-MOS Tutorial – channel formation (cont.)

Vgs >0 -> + charge on the gate, - charge attracted to the oxide, + charge chased away from the oxide

Vgs=Vt -> channel of negative charge forms under the oxide; the oxide is depleted of + charge; Vt = threshold voltage

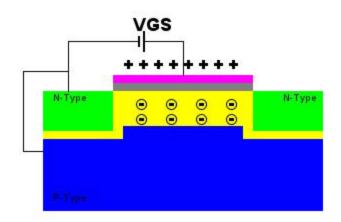

# N-MOS Tutorial – channel formation (cont.)

Vgs>Vt -> negative charge carriers form under the oxide; free electrons are thermally generated and form a conduction channel through which current can flow

• Vgs>Vt & Vds = 0 -> channel present, but no current flows

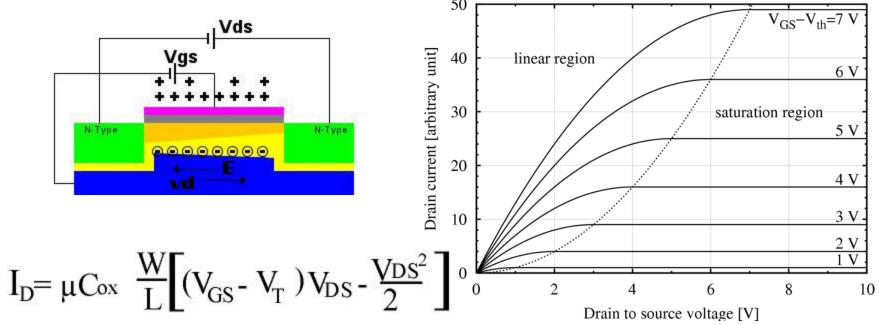

#### N-MOS Tutorial: Current flow

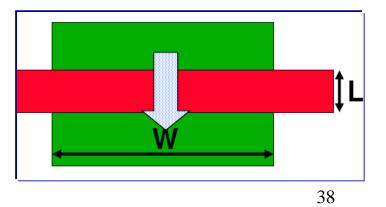

- Vds > 0 -> electric field (E) set up between source and drain, accelerates electrons with velocity vd, small current forms between source and drain

- Cox : oxide capacitance = ε<sub>ox</sub> / t<sub>ox</sub> (oxide permittivity ε<sub>ox</sub> and thickness t<sub>ox</sub>);

μ: mobility of charge carriers; W/L gate width and length

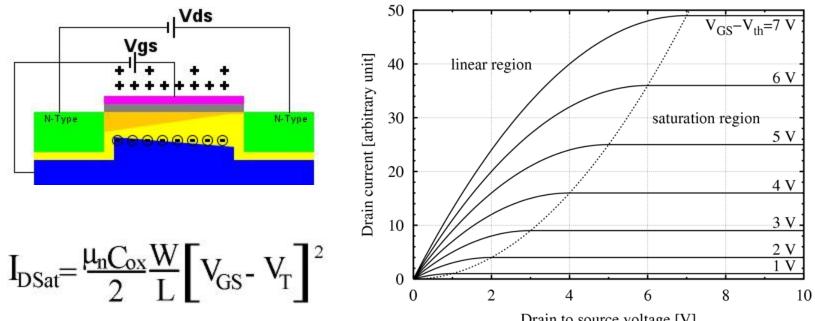

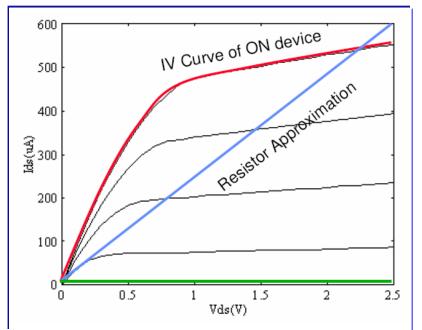

#### N-MOS Tutorial: Current flow

- Vds >= Vgs-Vt -> channel pinched off, saturated; constant current flows from drain to source

- Cox : oxide capacitance =  $\varepsilon_{ox}$  / tox (oxide permittivity  $\varepsilon_{ox}$  and thickness tox);  $\mu$ : mobility of charge carriers; W/L gate width and length

Drain to source voltage [V]

#### How about P-MOS?

- Everything is the same, but polarities of voltages reverse. Mobility () is 2x smaller, so 2x less current is generated if all other parameters are kept constant

- e.g. PMOS turns on when Vgs < Vt and both are <0

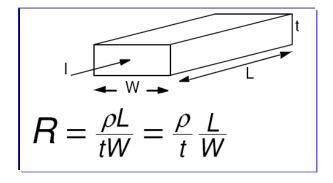

#### Resistance

- Resistivity

- Function of:

- resistivity r, thickness t : defined by technology

- Width W, length L: defined by designer

- Approximate ON transistor with a resistor

- R = r' L/W

- L is usually minimum; change only W

Source: Prof. Subhashish Mitra

#### Capacitance & Timing estimates

- Capacitor

- Stores charge Q = C V (capacitance C; voltage V)

- Current: dQ/dt = C dV/dt

- Timing estimate

- D t = C dV/ i = C dV / (V/R<sub>trans</sub>) = R<sub>trans</sub>C dV/V

• Delay: time to go from 50% to 50% of waveform