**Optimization of** Package Power **Delivery and Power Removal Solutions to** meet Platform level Challenges Kaladhar Radhakrishnan **Michael J. Hill** Kemal Aygün **Chia-Pin Chiu Gaurang Choksi**

### Agenda

$\bigcirc$

#### Metrology for Platform Level Power Delivery Characterization

New Power Delivery Architecture and Thermal Considerations for Multi-Core Servers

Recent Advances in Package Power Delivery and Power Removal Solutions

### Agenda

$\bigcirc$

#### Metrology for Platform Level Power Delivery Characterization

New Power Delivery Architecture and Thermal Considerations for Multi-Core Servers

Recent Advances in Package Power Delivery and Power Removal Solutions

### Enabling Platform Level Power Delivery Characterization

The Power Delivery Network

Time Domain Validation

What is Z(f)?

Measurement Setup

Application Examples

Status & Plans

\*Third party marks and brands are the property of their respective owners

Intel Developer

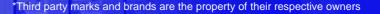

### **Typical Power Delivery Network**

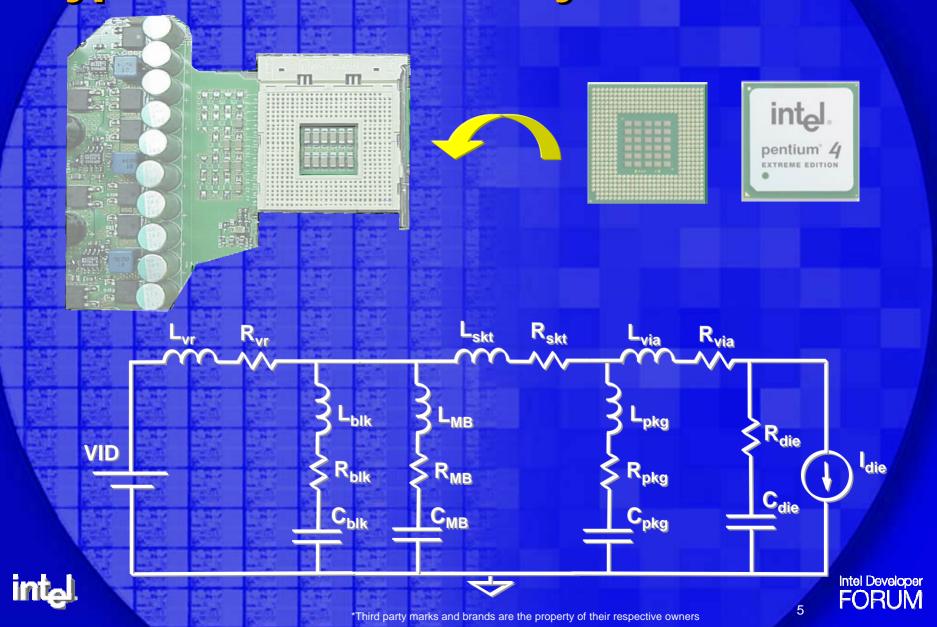

### **Time Domain Validation**

Voltage Transient Test (VTT) Tool

Test Platform

0

inte

#### **Loadline** = $\Delta V / \Delta I$

VTT tool is used as CPU emulator

Drawbacks with TD validation

VTT tool rise time different from that of processor

Not enough insight about the PD solution

\*Third party marks and brands are the property of their respective owners

Intel Developer

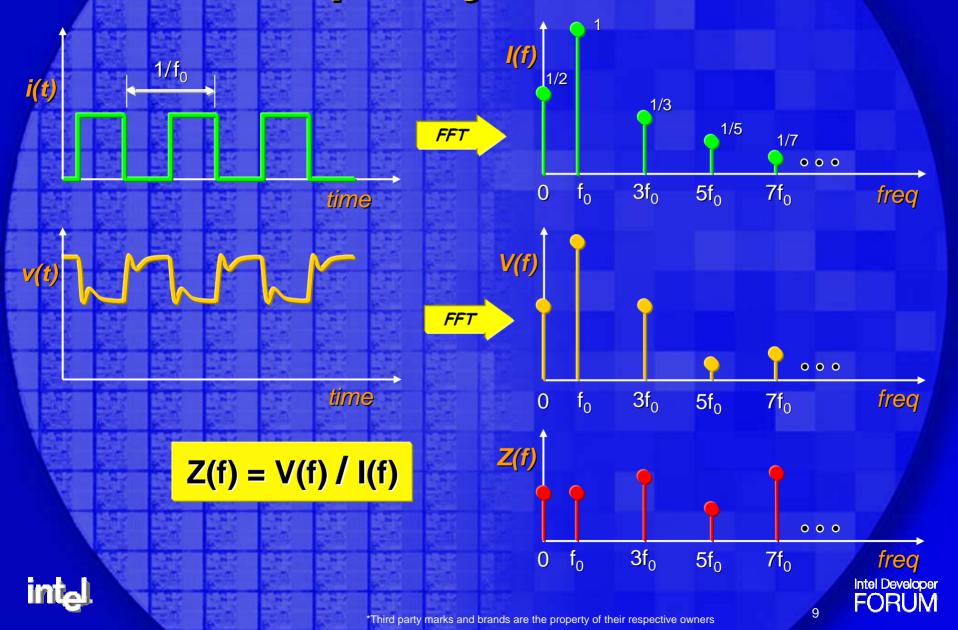

### What is Z(f)?

**VR Components**

Sink current from socket

Measure Voltage at MB sense pts.

## $V(f) = \frac{FFT}{v(t)}$ $I(f) = \frac{FFT}{i(t)}$

Fourier Transform can be used to determine frequency content of a time domain signal

Z(f)=V(f) / I(f)

Socket

Intel Developer

V(t)

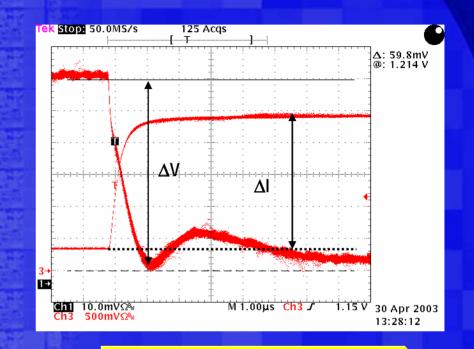

### Platform Z(f) – Measurement Setup

### **Time & Frequency Domains**

### **Time & Frequency Domains**

$f_1$  $3f_1$ 0  $5f_1$ time V(f) FFT time  $f_1$  $5f_1$ 0  $3f_1$ **Z(f)** Sweep frequency to populate the data points on the impedance profile plot  $3f_0 3f_1 5f_0 5f_17f_0$  $f_0 f_1$ 0

FFT

intel

i(t)

1/f<sub>1</sub>

\*Third party marks and brands are the property of their respective owners

**l(f)**

1/2

1/3

1/5

1/7

$7f_1$

$7f_1$

$7f_1$

10

• • •

• • •

• • •

freg Intel Developer

FORUM

freq

freg

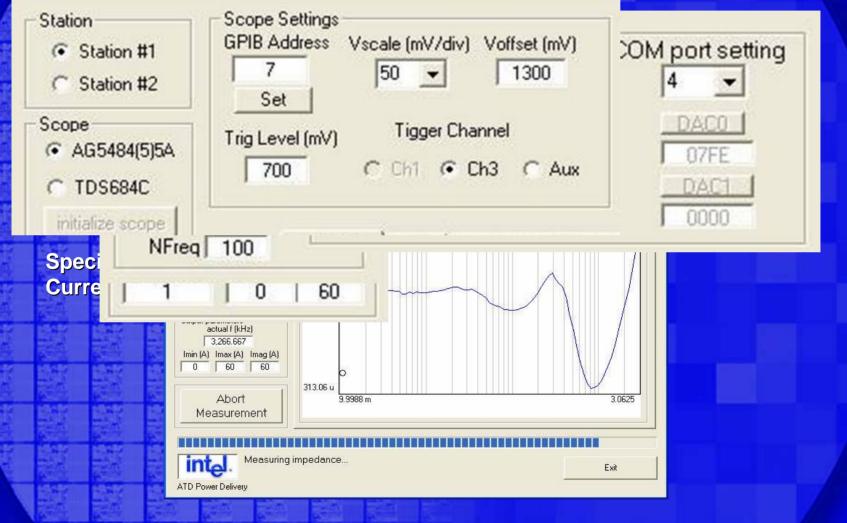

### Automation

intal

#### Platform Z(f) can be found in ~3-5 minutes

Intel Developer

11

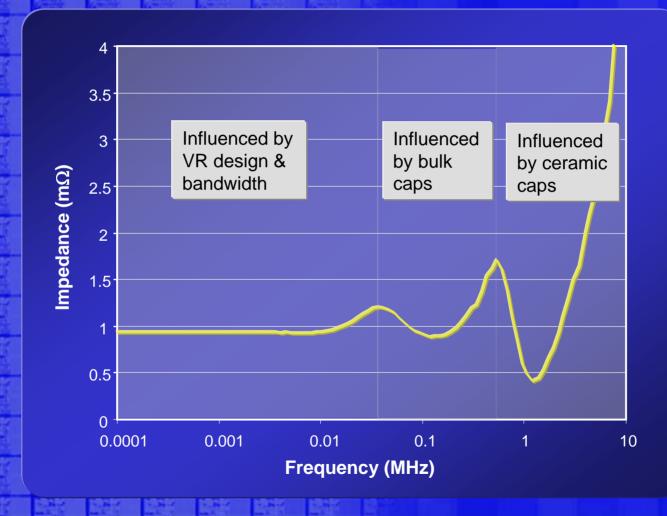

### Typical Platform Z(f)

intel

\*Third party marks and brands are the property of their respective owners

Intel Developer

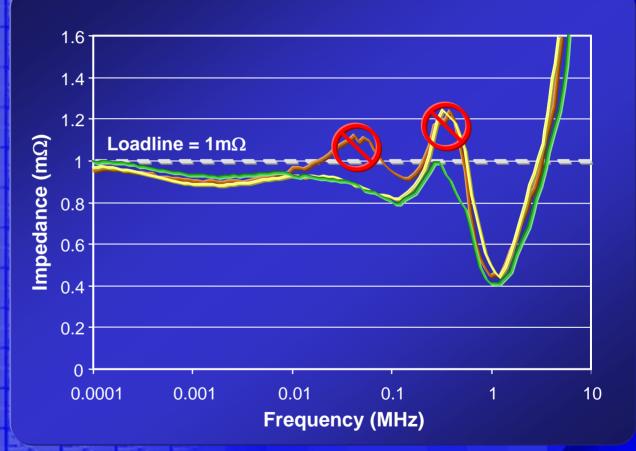

### Application – LGA775 platform

10 x 560 uF Bulk Caps 12 x 22 uF MLCC Caps

10 x 820 uF Bulk Caps 12 x 22 uF MLCC Caps

10 x 820 uF Bulk Caps 16 x 22 uF MLCC Caps 2 x 47uF MLCC Caps

inte

\*Third party marks and brands are the property of their respective owners

Intel Developer

FORUM

### **Status & Plans for OEM Deployment**

Setup and plans demonstrated to OEMs

Aug 5 Intel Power Summit at Dupont, WA

Customer version of the automation tool is currently being developed

- Tool will be designed to support different measurement setups using multiple scopes

- Automation tool will be made available to the OEMs along with the next release of the VTT tool

Intel Developer

### Summary

Capability developed for fully automated platform impedance profile measurements

Steps underway for deployment of measurement capability to OEMs

### Agenda

$\bigcirc$

Metrology for Platform Level Power Delivery Characterization

New Power Delivery Architecture and Thermal Considerations for Multi-Core Servers

Recent Advances in Package Power Delivery and Power Removal Solutions

### <u>Novel PD Architecture and Thermal</u> <u>Considerations for Multi-Core Servers</u>

Itanium Server PD Architecture

Xeon Server PD Architecture

Motivation for new architecture

New PD Scheme for Multi-Core Servers

Thermal Considerations

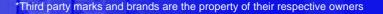

# Itanium Server PD Architecture

0

Power is supplied through a power pod Power is delivered through a topside power connector from one side of the package

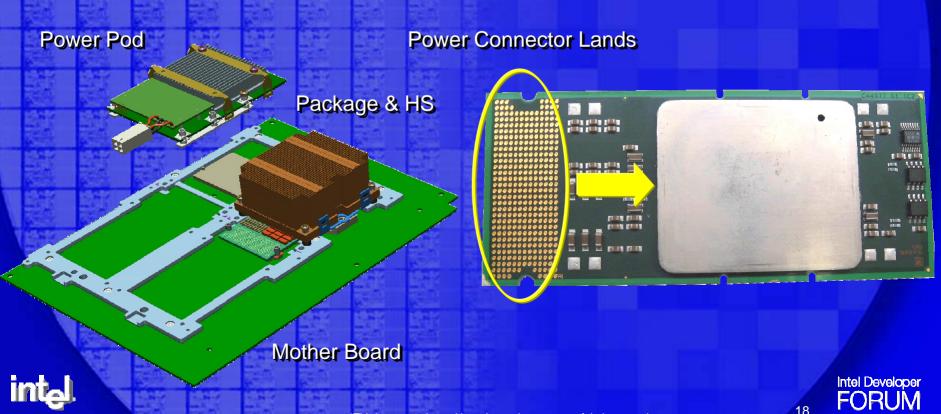

### Xeon Server PD Architecture

0

Power is supplied through pins on the socket Power is supplied from the voltage regulator through the pins from two sides on the package

### Motivation for New Architecture

- Power Delivery performance is limited with either PD architecture

- **MB Real Estate for Power Delivery**

0

0

0

Opportunity for synergy between the Xeon and Itanium servers

### **New Power Delivery Architecture**

**VR** Components

0

CPU & Package

**CPU Heatsink**

**VR Board & Heatsink**

**MB & Socket**

21

**CPU Heatsink**

int<sub>e</sub>l.

Backing Plate & Chassis Stiffener

\*Third party marks and brands are the property of their respective owners

Intel Developer

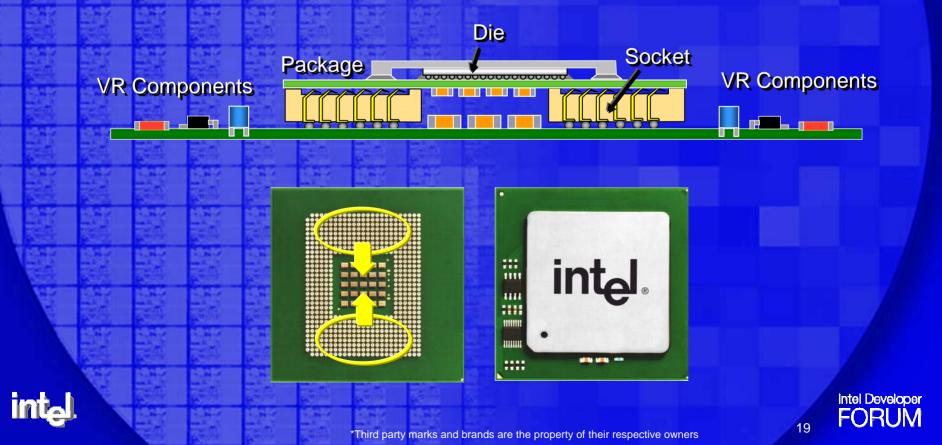

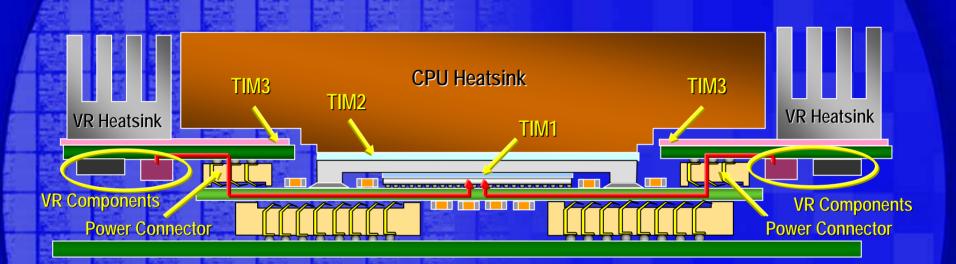

### New Architecture – Package Details

Four-sided power delivery scheme for improved performance

**Dedicated power connector is more scalable**

### **Cross-Section**

VR components moved to the VR board to free up MB real estate

New TIM3 material introduced to cool VR components

### **Thermal Considerations**

#### **CPU** Cooling

Increased die size due to multiple cores improves CPU cooling capacity

#### **VR** Components

- Increased power dissipation from the VR components due to the increasing current levels

- New TIM3 material introduced to keep VR component temperature under spec

#### **Power Connector**

- Joule heating in the power delivery path can drive up power connector temperature

- Need to contain maximum current through connector pins

0

•

0

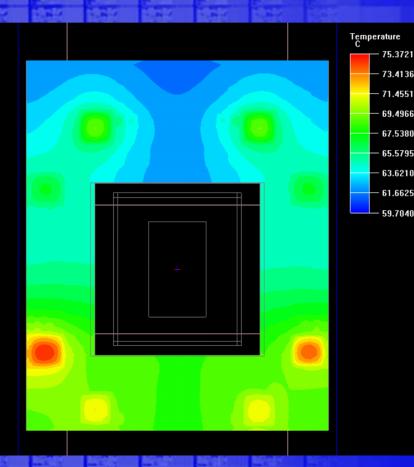

### **Thermal Analysis of the VR Board** Global model to obtain temperature distribution across VR board

inte

25

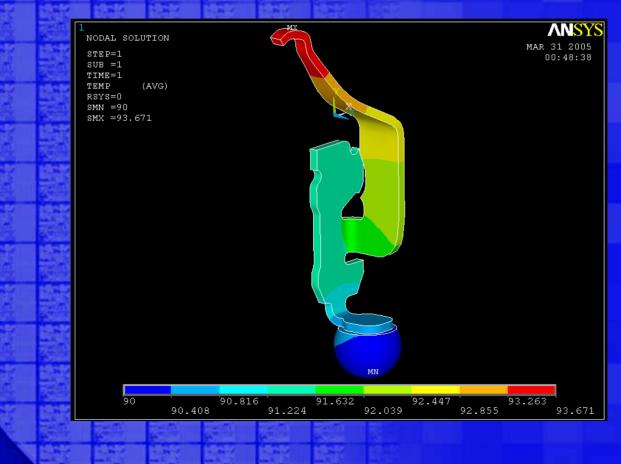

### Thermal Analysis of the Connector

Local model to estimate connector self-heating as a function of current through the pin

\*Third party marks and brands are the property of their respective owners

Intel Developer

### Summary

Novel PD architecture introduced for multicore servers

4 sided power delivery for better performance

- Dedicated power connector makes the new architecture more scalable

- Unified platform strategy for Xeon and Itanium server products

TIM3 material introduced to help keep VR and power connector temperature under spec

0

Intel Developer

### Agenda

$\bigcirc$

#### Metrology for Platform Level Power Delivery Characterization

New Power Delivery Architecture and Thermal Considerations for Multi-Core Servers

Recent Advances in Package Power Delivery and Power Removal Solutions

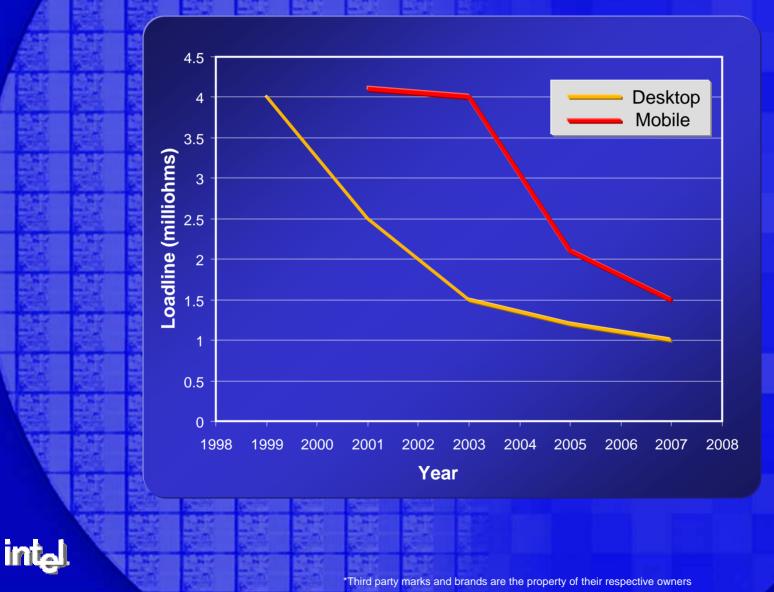

### **Advances in Package Power Delivery** and Power Removal Solutions **Desktop & Mobile Loadline Trends** 0 Evolution of Capacitors Advances in Socket Technology Package Technology Improvements Summary

29

int-

### **Desktop & Mobile Loadline Trends**

Intel Developer

### **Capacitor Technology**

0805 2T Capacitor

0805 IDC

0603 IDC

**Array Capacitor**

#### Capacitor technology has evolved over the years

- Transitioned from 2T capacitors to 0805 IDCs starting with processors in the 130 nm node

- Processors in the 65 nm node have started using 0603 IDCs

- Future generation processors could potentially use array capacitors if the technology warrants it

$\bigcirc$

31

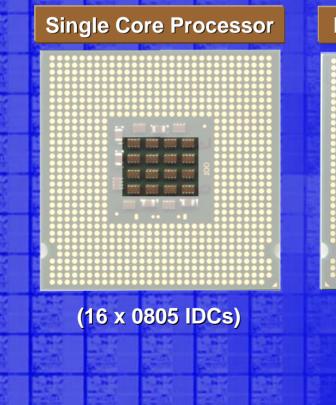

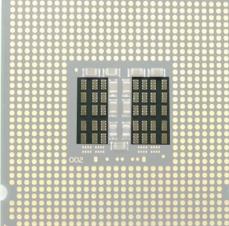

### **Capacitor** Example

0

inte

Reducing body size drives up capacitor count

**Dual Core Processor**

(35 x 0603 IDCs)

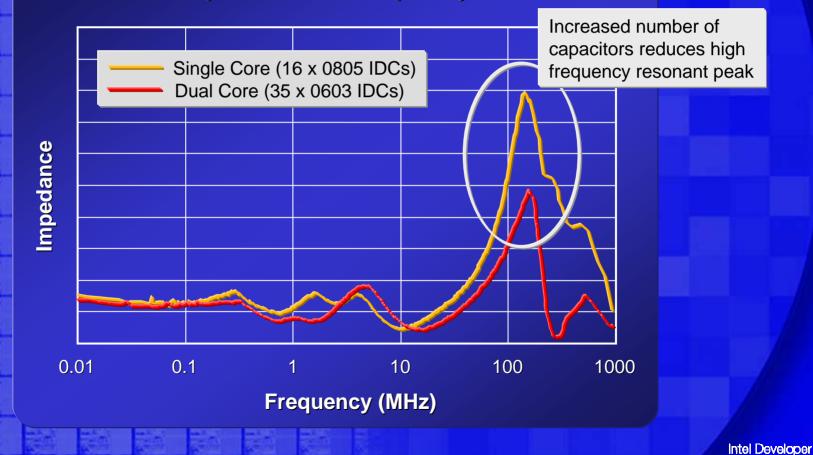

### Impedance Profile Comparison

#### Impedance vs. Frequency

\*Third party marks and brands are the property of their respective owners

FORI

### Socket Technology

Socket 370 49.5 x 49.5 mm

Socket 478 35 x 35 mm Socket 775 37.5 x 37.5 mm

34

Improvement in socket technology has enabled us to scale the pitch and fit more pins for a given area

### Package Resistance

0

#### 90nm Processor Package

0

inte

#### 65nm Processor Package

Packages for the 65nm processors have increased copper in the core layers to reduce resistance

Intel Developer

35

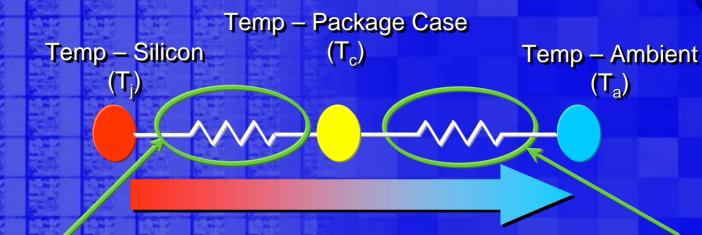

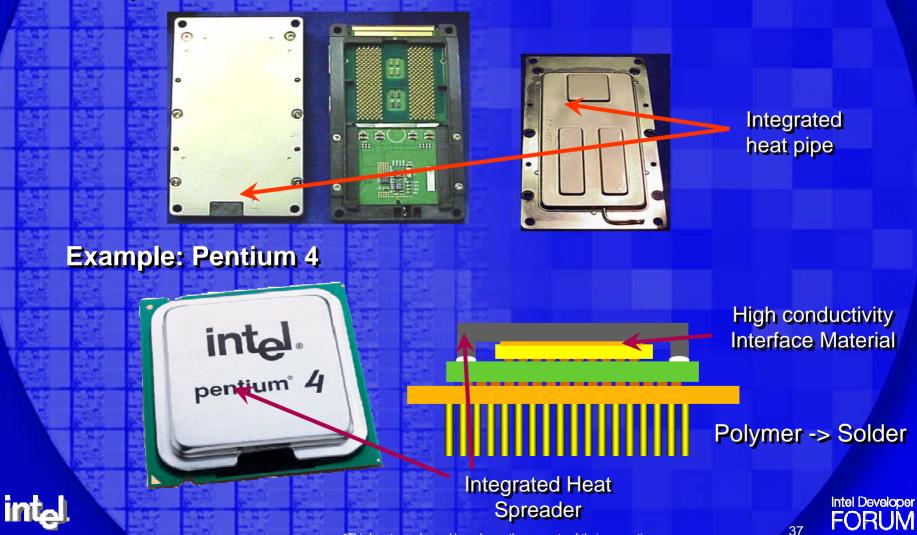

### **Power Removal Strategies**

#### **Temperature Gradient**

Packaging Smooth out Hot Spots

0

0

inte

**Packaging Strategy**

- Hot spot mitigation

- Reduction in thermal resistance (bulk & interface)

Heat Sink Strategy

– Material & Geometry Optimization

Cost effective manufacturability

Heatsink Duct out heat

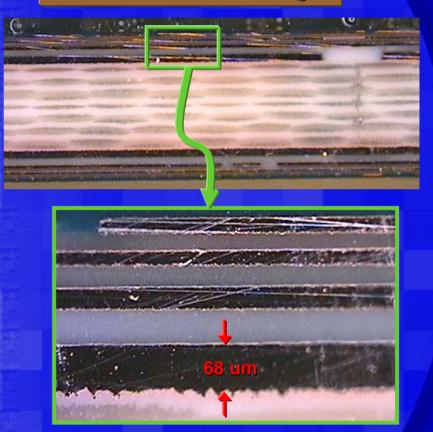

### Hot Spot mitigation

#### **Example:** Itanium

<sup>\*</sup>Third party marks and brands are the property of their respective owners

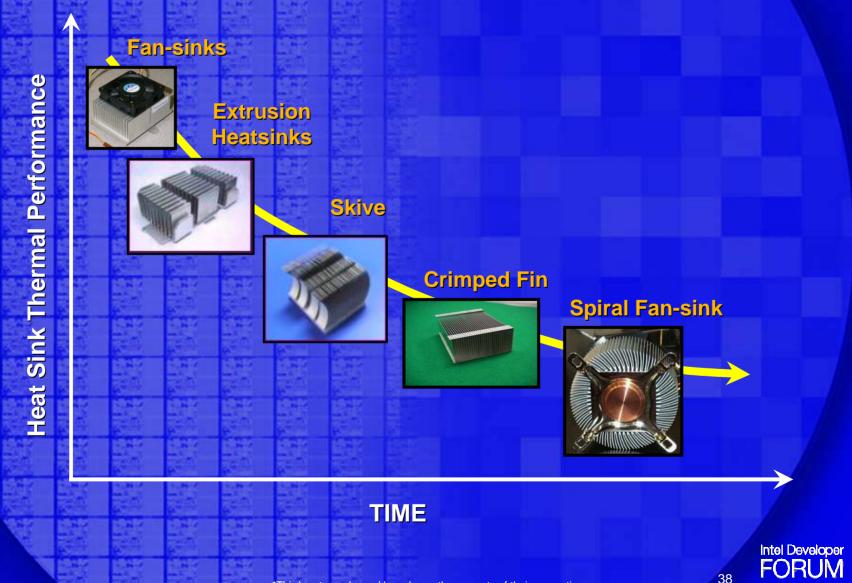

### Heat Sink Technology

intel

### Summary

The power delivery impedance target has been shrinking steadily over the years Capacitor technology has been steadily improving to address high frequency noise Improvements in socket and package technology help reduce DC resistance Use of the heat spreader and better TIM material have reduce package thermal resistance Heat sink technology has been improving to enhance cooling capability without driving up cost

Intel Developer

# Please fill out the Session Evaluation

Thank You!

Form

\*Third party marks and brands are the property of their respective owners