# Microprocessor Packaging

#### The Key Link in the Chain

Koushik Banerjee Technical Advisor Assembly Technology Development Intel Corporation

# Microprocessors

####

### **Global Packaging R&D**

#### Arizona Chandler

China Shanghai

Philippines Cavite

Malaysia Penang

### Virtual ATD

# Main R&D facility in Chandler, AZ

int<sub>el</sub>.

### Looking ahead ...

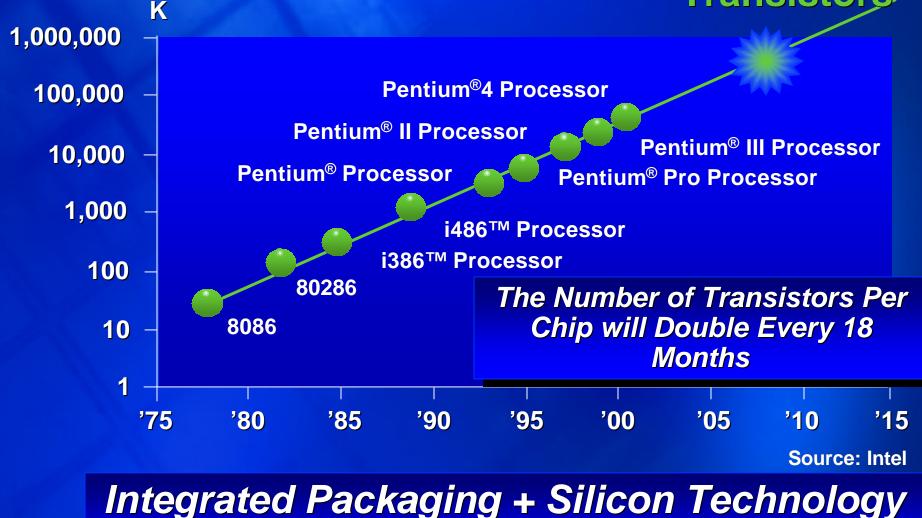

Complexity and Challenges to support Moore's Law

- **1.** Silicon to package interconnect

- 2. Within package interconnect

- **3.** Power management

- 4. Adding more functionality

Goal : Bring technology innovation into High volume manufacturing at a LOW COST

# Silicon & Package Relationship Anatomy 101

Silicon Processor: The "brain" of the computer (generates instructions)

Packaging: The rest of the body (Communicates instructions to the outside world, adds protection)

No Package = No Product ! Great Packaging = Great Products !!

# The Key Link in the Chain

Transistor-to-Transistor

Ckt Blk to Ckt Blk

**Opportunity** Innovative, efficient, high performance, lowcost packages are a significant competitive advantage

Chip-to-Package

Packageto-Board

Board-to-System

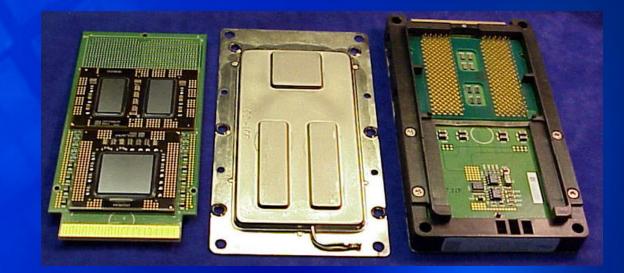

# Example – Enabling Custom solutions

#### Breaking Barriers to Moore's Law 1 Billion Transistors

development is essential

لمint

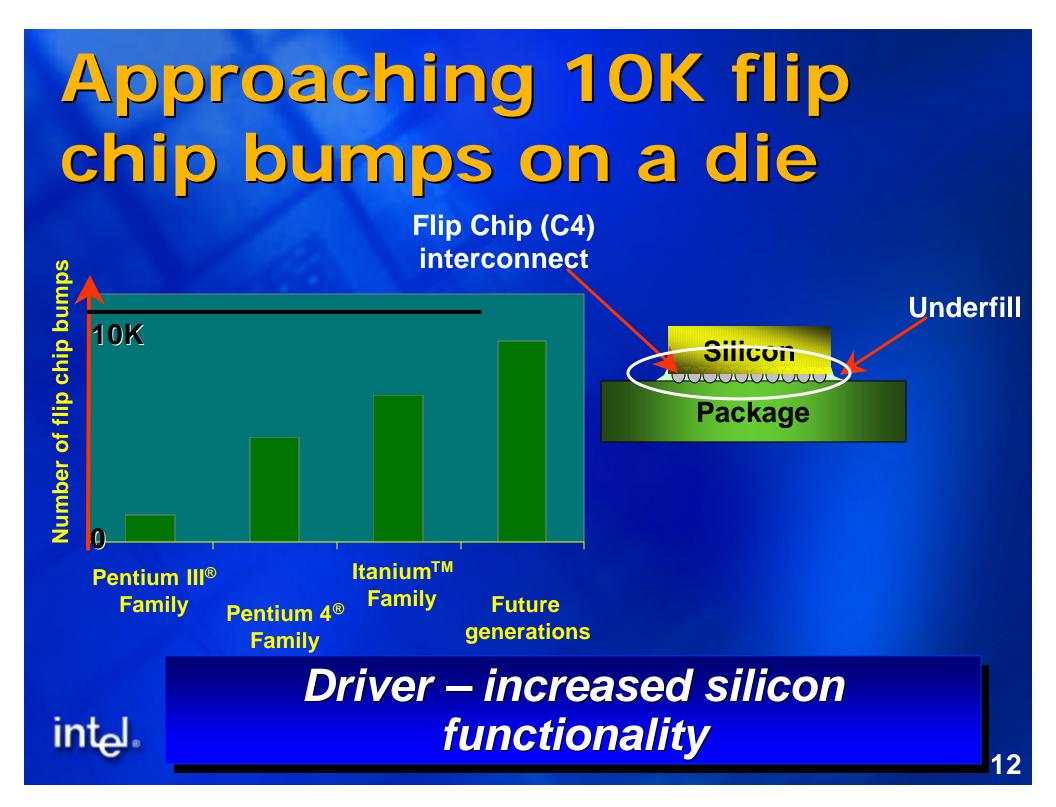

# Challenge # 1

# Silicon to package interconnect

int\_.

#### Solution : Aggressive Bump Pitch Scaling to keep down die size Solder Bumps

Human

Hair

Strand

- Plating bumps

- Chip Attach Process

- Underfill

- Joint integrity

- HVM scalable process

### Which leads us to ...

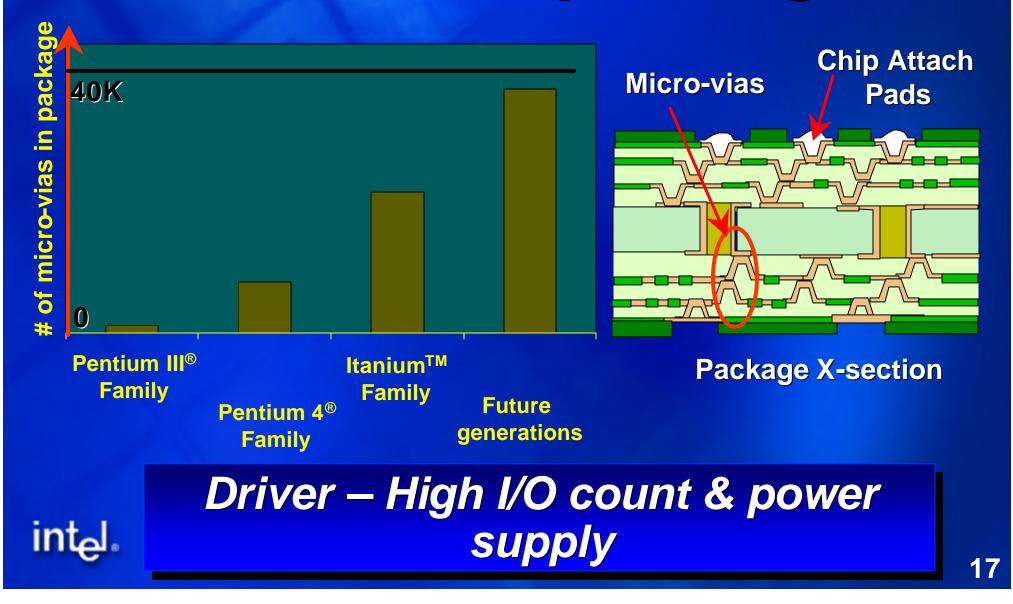

Challenge # 2

Within package Interconnect

int\_.

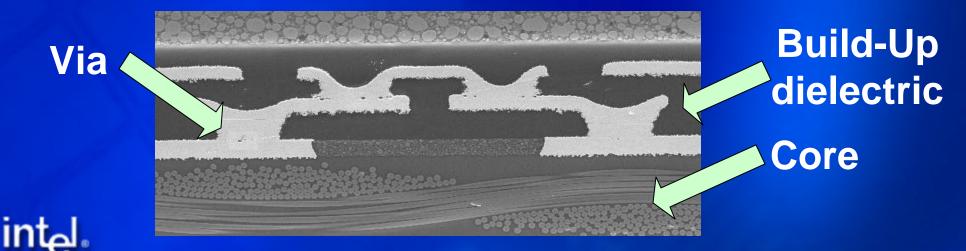

# Solution : High Density Interconnect

Very high escape routing density from the die

Package Traces

Lines narrowe

than hair

Human Hair

### Driver : Need high wiring density

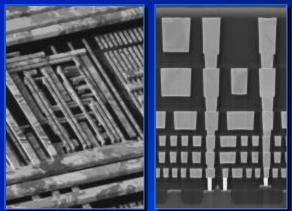

### **Dimensional Stack-Up**

Line in Silicon 130 nm (100X magnification)

Line in Package 25 um (100X magnification)

Line in Motherboard 5 mils (0.005") (100X magnification)

# Approaching 40K micro vias inside a package

# Solution : Advanced lithography (new term in packaging !)

# C/A pads

Key Challenges :

Developing HDI (high density interconnect) at LOW COST

High Volume Manufacturing Capable

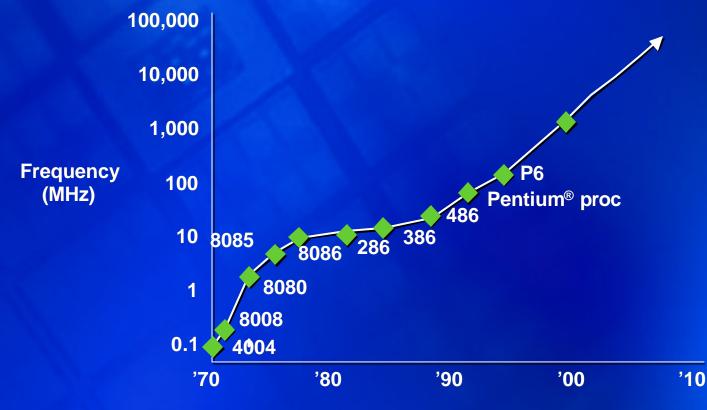

# Core frequency trend ... doubling every 2 years

Source : Intel Architecture Labs

In addition ...

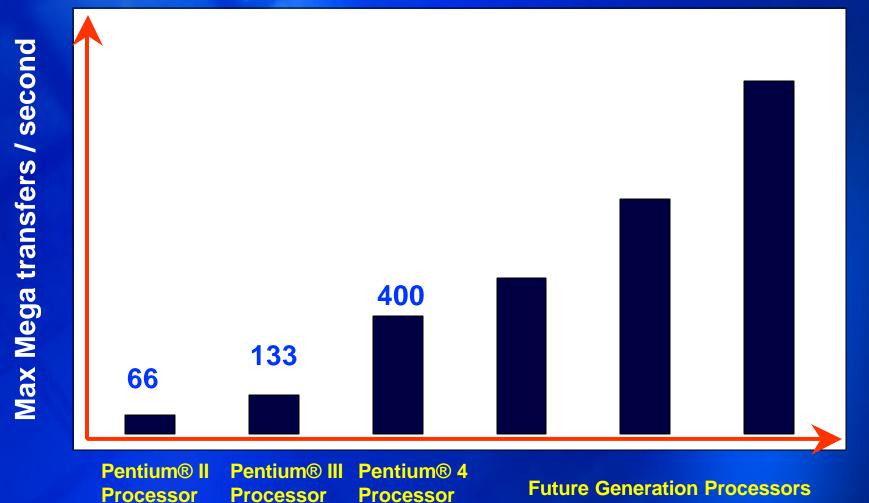

# FSB frequency ramp continues

int<sub>el</sub>.

#### **Microprocessor Generation**

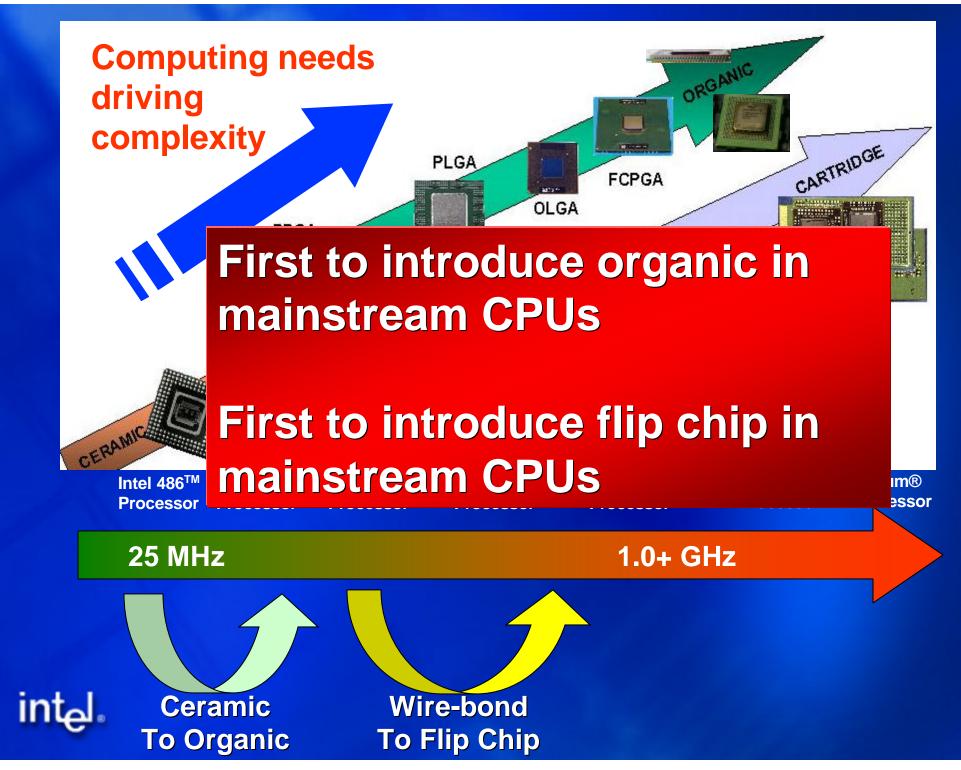

# Solution : High Performance Interconnect Technology Benefits of organic

- **1.** Copper Low resistance

- **2.** Low dielectric constant

- 3. <u>Cheaper</u>

# **Key Challenge :**

Optimize the entire substrate architecture (material properties, layer stack-up, via placement, power bussing etc.)

High Performance Silicon Copper Interconnects

**Organic Packaging**

### Solution : Better designs

# A poor design can ruin processor performance

### Key Challenges :

∠ Signal Timing

inte

- Innovative routing layout

- Solution Optimizing power / ground distribution

- Co-design of the complete silicon 🖉 package interconnect

# Switching gears from interconnect to ...

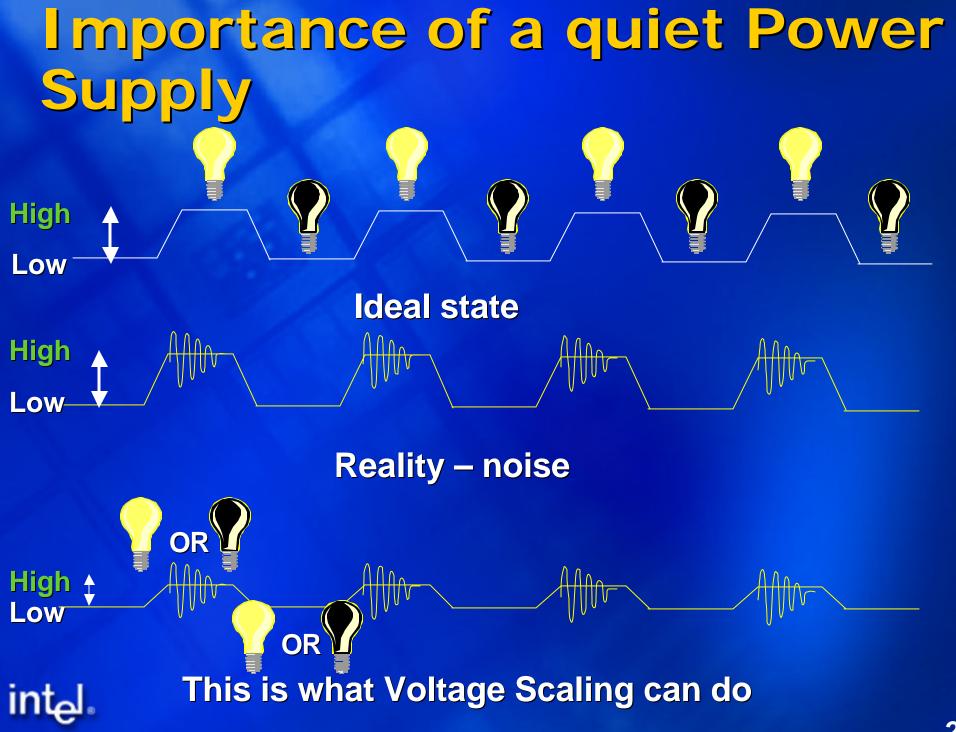

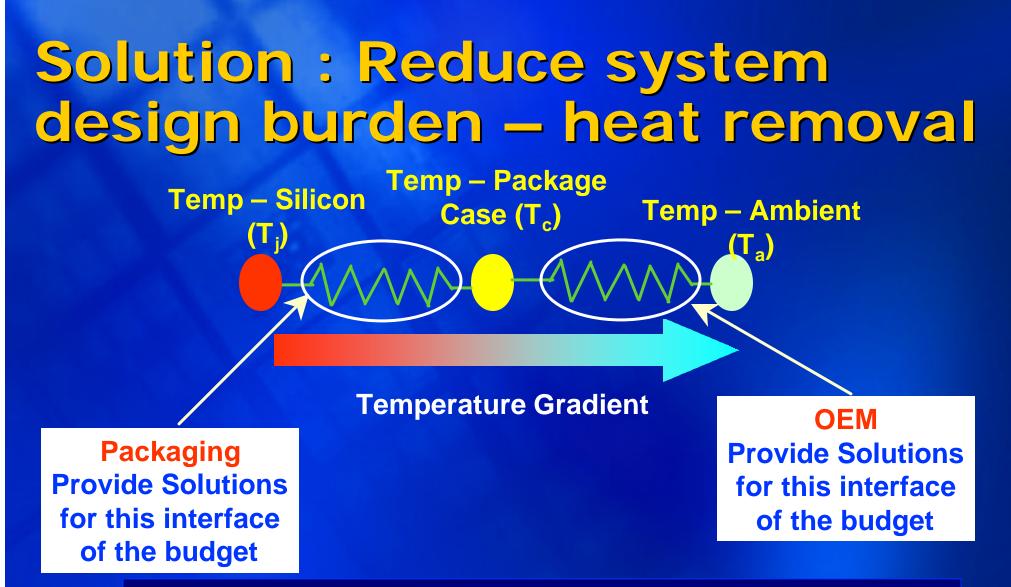

# Challenge # 3

# **Power Management**

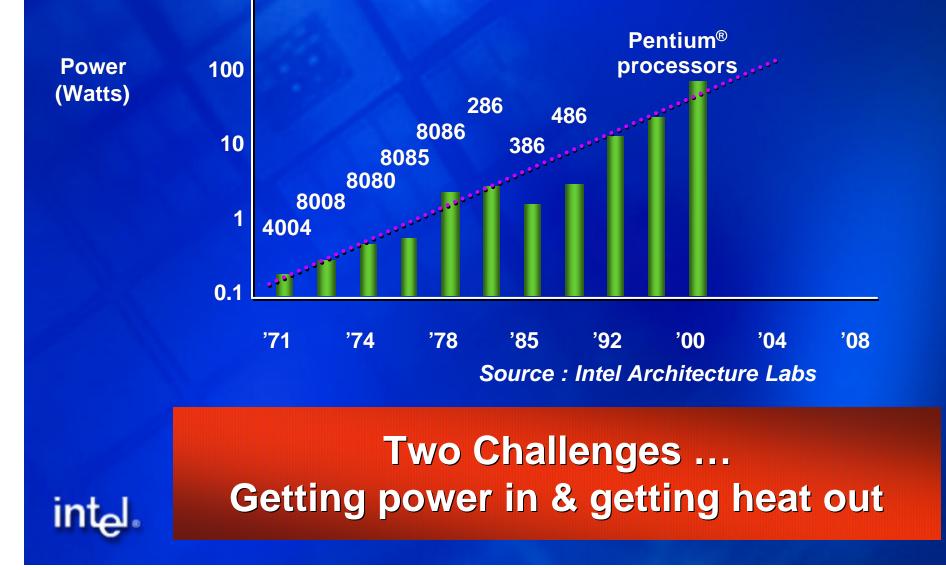

# Power Increasing, silicon getting smaller

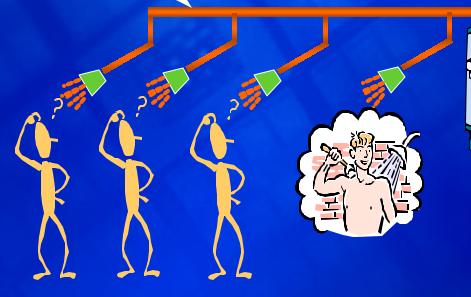

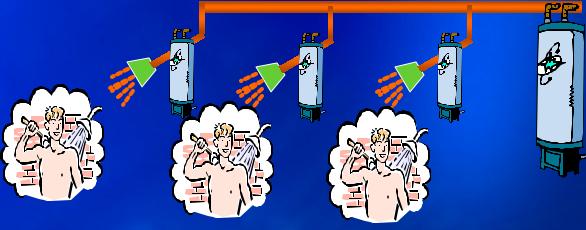

# Need lots of charge, very quickly ...

**Increasing distance from supply**

Hot Water Heater Inefficient design

Still Waiting !!

Close Proximity int<sub>e</sub>l. to supply

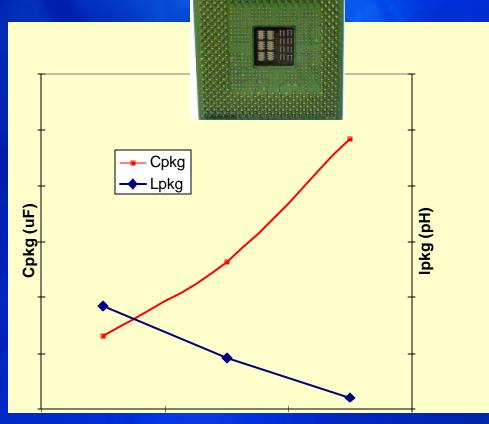

# Solution : Optimize design for power delivery

130 nm

Generation

processors

0.18 um Generation processors

int

Future Generation processors

### **Key Challenge:**

2X improvement in capacitance and inductance needed / generation

Need to optimize the complete silicon *k*

package integrated power delivery solution

Integrated Thermal Solutions in the package reduce heat flux – easier to cool in the system

into

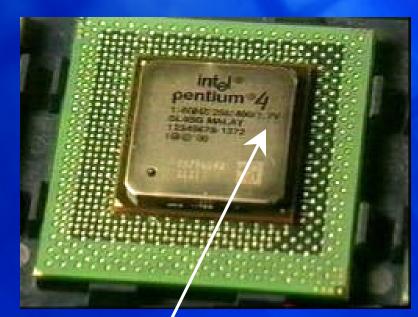

# Example : Pentium4®

High conductivity Thermal Interface Material

Integrated High Conductivity Heat – Spreader

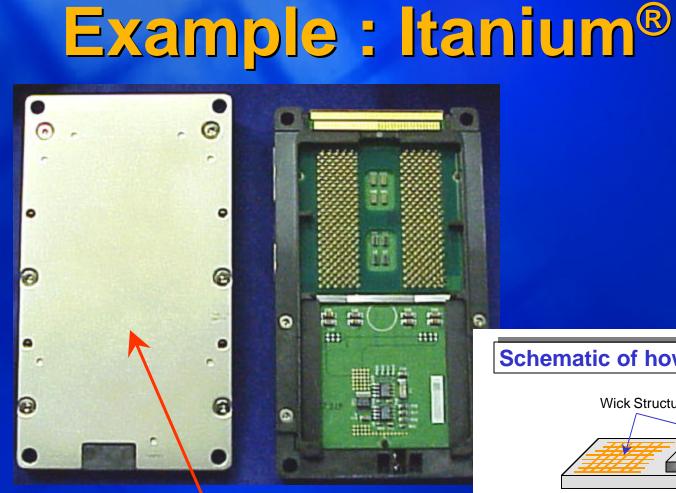

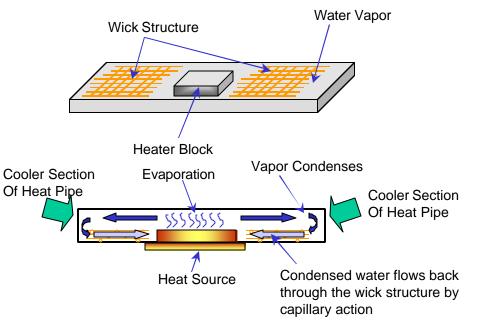

Integrated heat pipe technology interfacing directly to the silicon

#### Schematic of how a typical heat pipe works

50

And finally ...

# Challenge # 4

Adding more functionality

int\_.

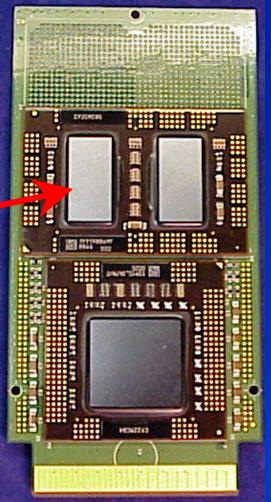

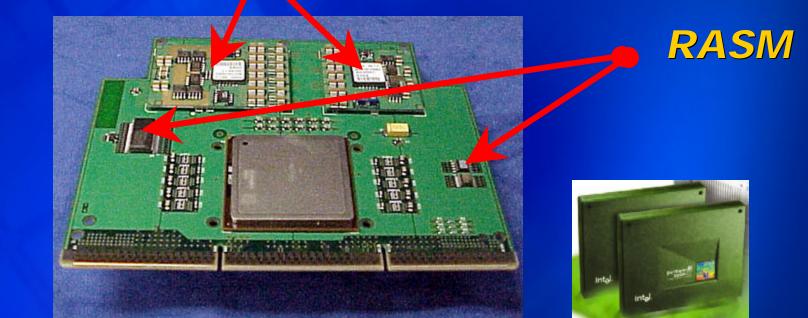

# Solution : High Density interconnect = more integration

High Density Interconnect enables a large cache memory integration in a small space

intപം

Leveraging packaging instead of adding onto silicon

## Solution : Massive integration = more features

# On CPU Voltage regulation

# In Summary ...

int<sub>el</sub>.

# We talked about future Complexity and Challenges to support Moore's Law

- **1.** Silicon to package interconnect

- 2. Within package interconnect

- **3.** Power management

- **4.** Adding more functionality

Intel's Packaging Strategy Innovative Technology Making Technology <u>Affordable</u> Smart designs Integrated silicon + packaging solutions

#### For more information, please visit ....